فهرست مطالب:

- مرحله 1: VHDL و Modelsim

- مرحله 2: کد VHDL برای طراحی و میز آزمایش

- مرحله 3: فایل های پیوست شده

- مرحله 4: IP IP کوتاه - 16 بیت

تصویری: الگوریتم قلبی با استفاده از VHDL: 4 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:52

بیشتر توسط نویسنده دنبال کنید: //www.linkedin.com/in/mitu

درباره: Mitu Raj - Just a Hobbyst and Learner - طراح تراشه - توسعه دهنده نرم افزار - علاقه مندان به فیزیک و ریاضیات بیشتر درباره AmCoder »

## این بیشترین پیوند ، محبوب ترین پیوند در Google برای پیاده سازی VHDL الگوریتم CORDIC برای ایجاد موج سینوسی و کسینوس است سالهای زیاد CORDIC چنین الگوریتمی است که چیزی نیست جز مجموعه ای از تغییرات و افزودن منطق هایی که برای محاسبه طیف وسیعی از توابع از جمله توابع مثلثاتی ، هذلولی ، خطی و لگاریتمی استفاده می شود. این الگوریتم مورد استفاده در ماشین حساب ها و غیره است. بنابراین تنها با استفاده از شیفترها و جمع کننده های ساده می توان سخت افزاری با پیچیدگی کمتر اما قدرت DSP با استفاده از الگوریتم صوتی طراحی کرد. از این رو می توان آن را به عنوان طرح RTL برهنه در VHDL یا Verilog بدون استفاده از واحدهای نقطه شناور اختصاصی یا IP های ریاضی پیچیده طراحی کرد.

مرحله 1: VHDL و Modelsim

در اینجا الگوریتم صوتی با استفاده از VHDL برای ایجاد موج سینوسی و موج سین پیاده سازی شده است. این می تواند سینوس و کسینوس از زاویه ورودی را با دقت بسیار بالا تولید کند. این کد در FPGA قابل سنتز است. Modelsim برای شبیه سازی طراحی و نیمکت آزمایش استفاده می شود.

مرحله 2: کد VHDL برای طراحی و میز آزمایش

تکنیک مقیاس دوتایی برای نشان دادن اعداد نقاط شناور استفاده می شود.

لطفاً قبل از کدگذاری ، از طریق اسناد پیوست بروید.

برو از طریق شبیه سازی cordic_v4.vhd - طراحی - ورودی زاویه در 32 بیت + بیت علامت است. می تواند هر زاویه ای را از 0 تا +/- 360 درجه با دقت ورودی 0.000000000233 درجه پردازش کند. هنگام دادن ورودی -> MSB بیت علامت است و بقیه 32 بیت نشان دهنده بزرگی است. -خروجی طرح مقدار سینوس و cos آن در 16 بیت + بیت علامت است. با دقت 0.00001526. لطفاً توجه داشته باشید که اگر مقدار سینوس یا cos مربوطه منفی باشد ، خروجی به شکل تعریف 2 نمایش داده می شود. شبیه سازی testb.vhd - نیمکت تست برای طراحی (1) زاویه های ورودی و بازنشانی کشش = '0'. پس از دو مرحله شبیه سازی ، مجدداً روی "1" و "همه را اجرا کنید" بازنشانی کنید. (2) در پنجره شبیه سازی ، شعاع سین و sin را به صورت اعشاری و فرمت> آنالوگ (خودکار) تنظیم کنید. (3) برای مشاهده شکل موج ، بزرگنمایی کنید. به درستی.

مرحله 3: فایل های پیوست شده

(1) cordic_v4.vhd - طراحی. (2) testb.vhd - نیمکت تست برای طراحی.

(3) سند نحوه اعمال نیرو به زاویه ورودی و تبدیل نتایج باینری.

به روز رسانی: این فایل ها فاقد هرگونه اطلاعاتی هستند و دیگر ارائه نمی شوند. لطفاً از فایل های بعدی از مرحله بعدی استفاده کنید

مرحله 4: IP IP کوتاه - 16 بیت

محدودیت پیاده سازی بالا- فرکانس پایین آهسته و پایین ساعت به دلیل انجام محاسبات در یک چرخه کلاک واحد است. IP هسته مینی کوردیک- 16 بیت

- مسیرهای حیاتی برای بهبود عملکرد به چرخه های مختلف توزیع شده است. قبلی. Testbench:

کاملا خودکار از 0 تا 360 درجه ورودی زاویه

فایل های پیوست شده: 1) مینی فایل اصلی vhdl 2) نیمکت تست مینی کوردیک 3) دفترچه راهنمای مینی Cordic IP 4) سند نحوه اعمال زوایا و تبدیل نتایج

برای هرگونه سوال ، با من تماس بگیرید:

میتو راج

مرا دنبال کنید:

ایمیل: [email protected]

### تعداد بارگیری ها: 325 تا 01-05-2021 ###

### آخرین ویرایش کد: ژوئیه -2020-07 ###

توصیه شده:

ربات خود متعادل - الگوریتم کنترل PID: 3 مرحله

ربات خود متعادل - الگوریتم کنترل PID: این پروژه به این دلیل طراحی شد که من علاقه مند بودم در مورد الگوریتم های کنترل و نحوه اجرای موثر حلقه های PID کاربردی بیشتر بیاموزم. این پروژه هنوز در مرحله توسعه است زیرا هنوز یک ماژول بلوتوث اضافه نشده است که

ماشین الگوریتم: 13 مرحله (همراه با تصاویر)

ماشین الگوریتم: من 15 سال است که علوم کامپیوتر را در سطح دانشگاه تدریس می کنم ، و اگرچه تخصص من بیشتر در زمینه برنامه نویسی است ، اما هنوز زمان زیادی را صرف پوشش الگوریتم های استاندارد برای جستجو و مرتب سازی می کنم. از دیدگاه آموزش

ECG Logger - مانیتور قلبی پوشیدنی برای جمع آوری و تجزیه و تحلیل داده های طولانی مدت: 3 مرحله

ECG Logger - مانیتور قلبی پوشیدنی برای دستیابی و تجزیه و تحلیل داده های بلند مدت: اولین انتشار: اکتبر 2017 آخرین نسخه: 1.6.0 وضعیت: پایدار دشواری: بالا پیش نیاز: Arduino ، برنامه نویسی ، ساخت سخت افزار مخزن منحصر به فرد: SF (پیوندهای زیر را ببینید) پشتیبانی: فقط انجمن ، no PMECG Logger یک مانیتور قلبی پوشیدنی برای مدت طولانی است

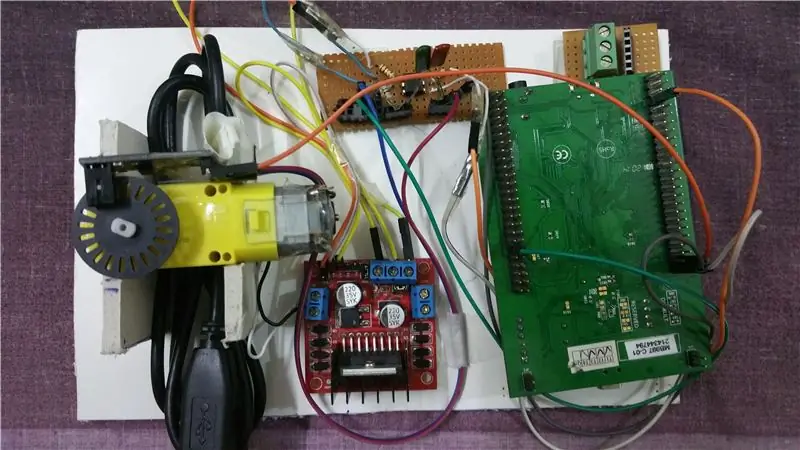

ربات خود متعادل با استفاده از الگوریتم PID (STM MC): 9 مرحله

ربات خود متعادل با استفاده از الگوریتم PID (STM MC): اخیراً کارهای زیادی در زمینه خود متعادل سازی اشیا انجام شده است. مفهوم متعادل سازی خود با تعادل پاندول معکوس آغاز شد. این مفهوم در طراحی هواپیماها نیز گسترش یافت. در این پروژه ، ما یک مد کوچک طراحی کرده ایم

کنترل سرعت موتور DC با استفاده از الگوریتم PID (STM32F4): 8 مرحله (همراه با تصاویر)

کنترل سرعت موتور DC با استفاده از الگوریتم PID (STM32F4): سلام به همه ، این طاهر الحق با پروژه دیگری است. این بار STM32F407 به عنوان MC است. این پایان پروژه نیمه ترم است. امیدوارم دوست داشته باشید. این نیاز به مفاهیم و نظریه های زیادی دارد ، بنابراین ابتدا به آن می پردازیم. با ظهور رایانه ها و