فهرست مطالب:

تصویری: طراحی یک کنترل کننده حافظه پنهان ساده چهار طرفه ساده در VHDL: 4 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:54

در دستورالعمل قبلی من ، ما نحوه طراحی یک کنترل کننده کش ساده نقشه برداری مستقیم را دیدیم. این بار ، ما یک قدم جلوتر حرکت می کنیم. ما در حال طراحی یک کنترل کننده حافظه پنهان مجموعه ای چهار طرفه ساده هستیم. مزیت - فایده - سود - منفعت ؟ کمتر از دست رفته ، اما به قیمت عملکرد. درست مانند وبلاگ قبلی من ، ما در حال طراحی و شبیه سازی کل پردازنده ، حافظه اصلی و محیط حافظه نهان برای آزمایش کنترلر حافظه پنهان هستیم. امیدوارم این را به عنوان یک مرجع مفید برای درک مفاهیم و طراحی کنترلرهای کش خود در آینده پیدا کنید. از آنجا که مدل پردازنده (نیمکت تست) و سیستم حافظه اصلی دقیقاً مشابه وبلاگ قبلی من هستند ، دیگر آنها را توضیح نمی دهم. لطفاً برای اطلاعات بیشتر در مورد آن به دستورالعمل قبلی مراجعه کنید.

مرحله 1: مشخصات

نگاهی سریع به مشخصات Cache Controller ارائه شده در اینجا:

- چهار طرفه تنظیم Associate Cache Controller (اگر به دنبال Direct Mapped Cache Controller هستید به این پیوند بروید).

- تک بانکی ، مسدود کردن حافظه پنهان.

- سیاست نوشتن از طریق نوشتن بازدیدها.

- Policy-Around Policy در نوشتن خطاهای نوشتاری.

- سیاست جایگزینی درخت شبه LRU (pLRU).

- آرایه برچسب درون کنترلر

- پارامترهای قابل تنظیم

مشخصات پیش فرض Cache Memory و Main Memory همان چیزی است که قبلاً قابل استفاده بود. لطفاً به آنها مراجعه کنید.

مرحله 2: نمای RTL کل سیستم

نمایش کامل RTL ماژول بالا در شکل (به استثنای پردازنده) نشان داده شده است. مشخصات پیش فرض اتوبوس ها عبارتند از:

- همه گذرگاه های داده باس های 32 بیتی هستند.

- Bus Bus = گذرگاه 32 بیتی (اما فقط 10 بیت در اینجا با حافظه قابل آدرس دهی است).

- بلوک داده = 128 بیت (گذرگاه پهنای باند گسترده برای خواندن).

- همه اجزا توسط یک ساعت حرکت می کنند.

مرحله 3: نتایج آزمایش

ماژول بالا با استفاده از یک Bench Test آزمایش شد که به سادگی یک پردازنده بدون لوله را شبیه سازی می کند ، درست مانند ما در دستورالعمل قبلی. میز تست درخواست های خواندن/نوشتن داده را به طور مکرر در حافظه ایجاد می کند. این دستورالعمل های معمولی "بار" و "ذخیره" را که در همه برنامه های اجرا شده توسط پردازنده رایج است به سخره می گیرد.

نتایج آزمایش عملکرد Cache Controller را با موفقیت تأیید کرد. در زیر آمار آزمون مشاهده شده است:

- همه خواندن/نوشتن سیگنال های Miss و Hit به درستی ایجاد شد.

- همه عملیات خواندن/نوشتن داده ها از هر چهار جهت موفق بود.

- الگوریتم pLRU با موفقیت برای جایگزینی خطوط حافظه پنهان تأیید شده است.

- هیچ مشکل ناسازگاری/ناسازگاری داده ها تشخیص داده نشد.

- زمان طراحی با موفقیت برای Maxm تأیید شد. فرکانس ساعت = 100 مگاهرتز در برد Xilinx Virtex-4 ML-403 (کل سیستم) ، 110 مگاهرتز تنها برای Cache Controller.

- RAM های بلوک برای حافظه اصلی استنباط شد. همه آرایه های دیگر بر روی LUT اجرا شد.

مرحله 4: فایل های پیوست شده

فایلهای زیر در اینجا با این وبلاگ ضمیمه شده است:

- . VHD فایل های Cache Controller ، Cache Data Array ، Main Memory System.

- نیمکت آزمون.

- مستندات مربوط به Cache Controller

یادداشت:

- برای درک کامل مشخصات Cache Controller که در اینجا ارائه شده است ، اسناد را مرور کنید.

- هرگونه تغییر در کد به سایر ماژول ها وابسته است. بنابراین ، تغییرات باید با دقت انجام شود.

- به همه نظرات و سرفصل هایی که من گفتم توجه کنید.

- اگر به هر دلیلی ، Block RAM ها برای حافظه اصلی استنباط نمی شوند ، اندازه حافظه را کاهش دهید و به دنبال آن در عرض گذرگاه آدرس در فایلها و غیره تغییر دهید. به طوری که همان حافظه را می توان در LUT یا RAM توزیع شده پیاده سازی کرد. این باعث صرفه جویی در زمان و منابع می شود. یا ، به اسناد خاص FPGA بروید و کد سازگار برای Block RAM را بیابید و کد را متناسب با آن ویرایش کنید و از مشخصات عرض عرض گذرگاه آدرس استفاده کنید. تکنیک مشابه برای Altera FPGA.

توصیه شده:

کنترل کننده نور اتوماتیک اتاق و فن با شمارنده بازدید کننده دو طرفه: 3 مرحله

کنترل کننده اتوماتیک نور اتاق و فن با شمارنده دو طرفه بازدیدکنندگان: اغلب شاهد پیشخوان بازدیدکنندگان در استادیوم ، مرکز خرید ، ادارات ، اتاق های کلاس و غیره هستیم. چگونه مردم را می شمارند و چراغ را روشن یا خاموش می کنند در حالی که هیچکس داخل خانه نیست؟ امروز ما با پروژه کنترل اتوماتیک نور اتاق با پیشخوان بازدید کننده دو طرفه اینجا هستیم

طراحی یک کنترل کننده وقفه قابل برنامه ریزی در VHDL: 4 مرحله

طراحی یک کنترل کننده وقفه قابل برنامه ریزی در VHDL: من از نوع پاسخ هایی که در این وبلاگ دریافت می کنم غرق شده ام. بچه ها از اینکه به وبلاگ من سر زدید و انگیزه ای برای به اشتراک گذاشتن دانش خود با شما داشتم ، متشکرم. این بار ، من قصد دارم طراحی یک ماژول جالب دیگر را که در همه SOC ها مشاهده می کنیم - Interrupt C

طراحی یک کنترل کننده حافظه پنهان ساده در VHDL: 4 مرحله

طراحی یک کنترل کننده حافظه پنهان ساده در VHDL: من این را به صورت آموزشی می نویسم ، زیرا برای یادگیری و شروع به طراحی یک کنترل کننده حافظه پنهان ، دریافت کد مرجع VHDL کمی مشکل بود. بنابراین من خودم یک کنترلر حافظه پنهان را از ابتدا طراحی کردم و آن را با موفقیت روی FPGA آزمایش کردم. من p دارم

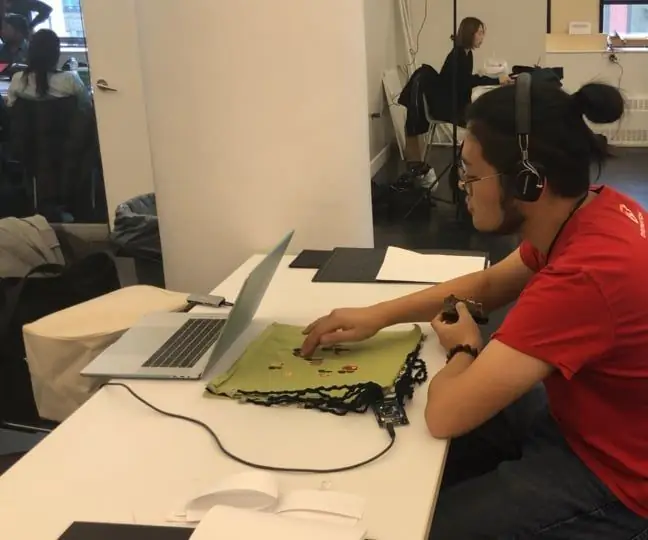

فضای پنهان - یک کنترل کننده بازی صوتی: 5 مرحله (همراه با تصاویر)

Hidden Space - an Audio Game Controller: در این آموزش ، ما یک کنترلر بازی برای یک بازی صوتی می سازیم. این بازی با Unity توسعه یافته است. در حال تلاش برای ایجاد یک رابط بازی خارج از صفحه نمایش ، با اطلاعات بصری و عمدتا صوتی محدود است. بازیکن لباس می پوشد

کلیدهای سه طرفه و چهار طرفه-نحوه عملکرد: 6 مرحله

سوئیچ های سه طرفه و چهار طرفه-نحوه عملکرد: در حالی که یک سوئیچ سه طرفه برای بسیاری از کسانی که از Instructables.com دیدن می کنند بسیار ساده است ، اما برای بسیاری دیگر یک راز است. درک نحوه عملکرد مدار کنجکاوی را برآورده می کند. همچنین می تواند به تشخیص یک سوئیچ سه طرفه کمک کند که کار نمی کند زیرا کسی