فهرست مطالب:

- مرحله 1: مشخصات

- مرحله 2: مروری بر PIC

- مرحله 3: طراحی و پیاده سازی RTL

- مرحله 4: نکات مهم و فایلهای پیوست

تصویری: طراحی یک کنترل کننده وقفه قابل برنامه ریزی در VHDL: 4 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:54

من از نوع پاسخ هایی که در این وبلاگ دریافت می کنم غرق شده ام. بچه ها از اینکه به وبلاگ من سر زدید و انگیزه ای برای به اشتراک گذاشتن دانش خود با شما داشتم ، متشکرم. این بار ، من قصد دارم طراحی یک ماژول جالب دیگر را که در همه SOC ها می بینیم - Interrupt Controller ، ارائه دهم.

ما در حال طراحی یک کنترل کننده وقفه برنامه نویسی ساده و در عین حال قدرتمند هستیم. این یک طراحی کاملاً قابل تنظیم و پارامتر بندی شده است که در سراسر سیستم عامل ها قابل حمل است. من این را پس از خواندن بسیاری از معماری های کنترل کننده وقفه معروف مانند NVIC ، 8259a ، RISC-V PLIC ، Microblaze's INTC و غیره طراحی کردم. امیدوارم این وبلاگ برای شما مفید باشد و به شما کمک می کند طعم نحوه مدیریت وقفه ها توسط پردازنده را بشناسید. با کمک کنترل کننده وقفه

مرحله 1: مشخصات

مشخصات IP به شرح زیر است:

- رابط AHB3-Lite

-

پارامترهای قابل تنظیم از نظر آماری:

- تعداد منابع وقفه خارجی ؛ تا 63 وقفه را پشتیبانی می کند.

- تعداد سطوح اولویت دار ؛ پشتیبانی تا 63 سطح

- تعداد سطوح لانه سازی ؛ تا 8 سطح لانه سازی را پشتیبانی می کند.

- عرض اتوبوس؛ 32 یا 64

- وقفه های قابل پوشش جهانی و محلی.

- سطح اولویت به طور پویا برای هر وقفه قابل تنظیم است.

- دو حالت عملکرد - حالت کاملاً تو در تو و حالت اولویت برابر.

- از وقفه های حساس فعال در سطح بالا پشتیبانی می کند.

مشخصات RISC-V PLIC با الهام از مکانیسم دست دادن در طراحی مورد استفاده قرار گرفته است.

قبل از انتخاب وقفه از 8259a الهام گرفته شده است

سایر مطالب: Microblaze INTC، NVIC

مرحله 2: مروری بر PIC

کنترل کننده وقفه قابل برنامه ریزی (PIC) وقفه های متعددی را از لوازم جانبی خارجی دریافت کرده و آنها را در یک خروجی وقفه واحد به هسته پردازنده مورد نظر ادغام می کند.

PIC از طریق کنترل های ثبت و وضعیت کنترل می شود. همه ثبت های PIC به صورت نقشه نگاشته شده و از طریق رابط گذرگاه AHB3-Lite قابل دسترسی است.

بانک ثبت شامل پیکربندی ثبت ، فعال کردن رجیسترها ، رجیسترهای در حال انتظار ، رجیسترهای در حال خدمت ، رجیسترهای اولویت دار و ثبت کننده شناسه است که در کنترل کننده های وقفه معمولی هستند.

ثبت تنظیمات برای تنظیم حالت عملکرد PIC استفاده می شود. این می تواند در حالت کاملاً تو در تو یا حالت اولویت برابر کار کند.

به هر وقفه می توان اولویت ها اختصاص داد و به صورت جداگانه پوشانده شد. پوشش جهانی همه وقفه ها نیز پشتیبانی می شود.

بانک ثبت با Priority Resolver و BTC (Binary-Tree-Comparator) تعامل دارد تا اولویت های وقفه های معلق را برطرف کرده و بر این اساس وقفه را به پردازنده اعلام کند. شناسه ثبت شامل شناسه وقفه ای است که دارای بالاترین اولویت است.

مرحله 3: طراحی و پیاده سازی RTL

طراحی PIC بر کاهش تأخیر در حل اولویت ها تأکید می کند ، که از نظر زمانی مهمترین بخش طراحی است. از آنجا که طراحی اولویت ها را در یک چرخه کلاک واحد حل می کند ، عملکرد با افزایش تعداد منابع با پیچیدگی Log2 کاهش می یابد.

این طرح با موفقیت اجرا شد و زمان تا فرکانسهای زیر در Artix-7 FPGAs تأیید شد.

- حداکثر تا 15 منبع: 100 مگاهرتز

- حداکثر 63 منبع: 50 مگاهرتز

تأخیر وقفه که فقط توسط PIC اضافه می شود 3 چرخه ساعت است (بدون در نظر گرفتن زمان تغییر زمینه پردازنده و اولین زمان واکشی دستورالعمل ISR).

مرحله 4: نکات مهم و فایلهای پیوست

یادداشت های مهم:

- اگر رابط AHB3-Lite نامطلوب است ، می توانید ماژول بالا را تغییر دهید و از طرح اسکلت PIC استفاده کنید. با این حال ، میز آزمایش ارائه شده برای IP با رابط AHB3-Lite است.

- PIC IP v1.0 یک طرح RTL کاملاً قابل حمل و برهنه است.

- عملکردی تأیید شده است که روی هر دو حالت کار می کند.

فایل های پیوست شده:

- طراحی کدها و میز آزمایش در VHDL.

- مستندات IP کامل

این یک طراحی منبع باز است … در صورت تمایل از آن استفاده کنید …

برای هر گونه پرسش ، در هر زمان:

میتو راج

توصیه شده:

طراحی یک کنترل کننده حافظه پنهان ساده چهار طرفه ساده در VHDL: 4 مرحله

طراحی یک کنترل کننده ساده راهپیمایی چهار طرفه ساده در VHDL: در دستورالعمل قبلی من ، نحوه طراحی یک کنترل کننده کش ساده نقشه برداری مستقیم را دیدیم. این بار ، ما یک قدم جلوتر حرکت می کنیم. ما در حال طراحی یک کنترل کننده حافظه پنهان مجموعه ای چهار طرفه ساده هستیم. مزیت - فایده - سود - منفعت ؟ نرخ از دست دادن کمتر ، اما به قیمت انجام

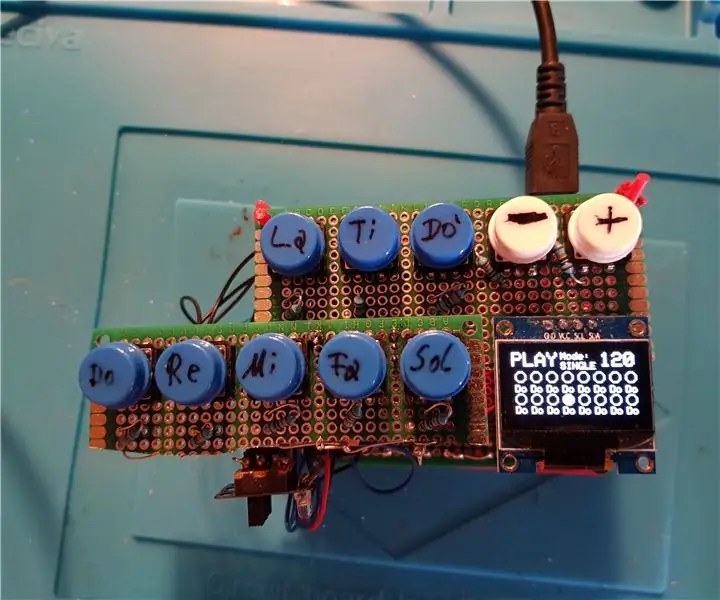

DoReMiQuencer - دنبال کننده MIDI قابل برنامه ریزی با صفحه کلید: 7 مرحله

DoReMiQuencer - MIDI Sequencer قابل برنامه ریزی با صفحه کلید: این دستگاه برای استفاده با VCVRack ، یک سینت سایزر ماژولار مجازی که توسط VCV ایجاد شده است ، ایجاد شده است ، اما می تواند به عنوان یک کنترل کننده MIDI عمومی مورد استفاده قرار گیرد. بسته به حالت انتخاب شده ، به عنوان دنبال کننده یا صفحه کلید MIDI عمل می کند. یادداشت های MIDI بر روی ke

هنر دو بعدی با LED های قابل برنامه ریزی و پایه و لوگوی قابل تنظیم: 5 مرحله (همراه با تصاویر)

هنر دو بعدی با LED های قابل برنامه ریزی و پایه و لوگوی قابل برنامه ریزی: به دستورالعمل خوش آمدید! امروز ، من به شما نحوه ساخت یک پروژه هنری دو بعدی با لوگو و طرح کلی دلخواه خود را نشان خواهم داد. من این پروژه را ساختم زیرا می تواند مهارت های زیادی مانند برنامه نویسی ، سیم کشی ، مدل سازی سه بعدی و موارد دیگر را به مردم آموزش دهد. این

ماز لیزری قابل برنامه ریزی با آردوینو و برنامه اندروید: 13 مرحله (همراه با تصاویر)

پیچ و خم لیزری قابل برنامه ریزی با آردوینو و برنامه اندروید: تعداد زیادی پیچ و خم از کتاب های بچه ها گرفته تا روبات حل اتوماتیک پیچ و خم را مشاهده کنید. در اینجا من چیزی را متفاوت امتحان می کنم که در آن پیچ و خم را با استفاده از بازتاب لیزری حل می کنم. هنگامی که در ابتدا فکر می کنم بسیار آسان است ، اما انجام آن ارزان ، هزینه زمان بیشتری برای دقت دارد. اگر کسی می خواهد به

تغذیه کننده ماهی آکواریوم قابل برنامه ریزی - غذای دانه بندی شده طراحی شده: 7 مرحله (همراه با تصاویر)

تغذیه کننده ماهی آکواریومی قابل برنامه ریزی - غذای دانه بندی شده طراحی شده: تغذیه کننده ماهی - غذای دانه بندی شده برای ماهیان آکواریومی طراحی شده است. طراحی بسیار ساده آن تغذیه کننده ماهی به صورت تمام اتوماتیک است. این دستگاه با میکرو سروو کوچک 9G SG90 و آردوینو نانو کار می کند. شما تغذیه کننده کامل را با کابل USB (از شارژر USB یا پورت USB دستگاه خود