فهرست مطالب:

- مرحله 1: تنظیم پروژه در Vivado برای ارنی

- مرحله 2: ایجاد PWM ارنی در Vivado

- مرحله 3: ایجاد TDOA ارنی در Vivado

- مرحله 4: بسته بندی و صادرات Ernie

- مرحله 5: ساختن ارنی

- مرحله 6: اولین BSP ارنی

- مرحله 7: FreeRTOS'ing Ernie

- مرحله 8: وارد کردن کد C Ernie

- مرحله 9: اشکال زدایی ارنی

- گام دهم: ایجاد خودمختاری ارنی

- مرحله 11: ساختن ارنی ناز

تصویری: طرز تهیه ارنی: 11 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:52

این یک آموزش در مورد چگونگی ساخت Ernie ، ربات صدای مستقل شما ، با استفاده از یک برد Zybo است. این شامل چگونگی: ایجاد پروژه در Vivado ، ایجاد درایورهای سرو موتور شبیه به PWM در FPGA ، رابط کاربری با دو سنسور صدا ، ایجاد تفاوت زمانی در IP ورود ، استفاده از freeRTOS ، و اجرای zybo از یک بسته باتری است. این آخرین پروژه ما برای کلاس سیستم عامل های زمان واقعی (CPE 439) در Cal Poly SLO بود.

لیست تجهیزات:

- 1 - برد توسعه ZYBO Zynq 7000

- 2 - سروال چرخشی مداوم Parallax

- 2 - سنسور صدا (آشکارساز صدا SparkFun)

- بسته باتری 1 - 5 ولت لیتیوم یون (برای برد)

- 4 - باتری AA (برای سرو)

- 1 - بسته باتری AA (بدون 4 اسلات باتری)

- 1 - کابل میکرو USB

- 1 - تخته نان

- بسیاری - سیم های نر به نر

- 1 - شاسی سروو

الزامات نرم افزاری:

- مجموعه طراحی Xilinx Vivado 2016.2

- Digilent Adept 2.16.1

مرحله 1: تنظیم پروژه در Vivado برای ارنی

- جادوگری ظاهر می شود

- Next را کلیک کنید

-

نام بعدی پروژه

- هرگز از نام پروژه یا مسیر دایرکتوری که دارای فاصله در آن است استفاده نکنید !!!!!

- این یک پروژه RTL خواهد بود.

- ما نمی خواهیم منابع را مشخص کنیم

-

با کلیک بر روی Next ، به صفحه Part می رسیم. ما از ZYNQ XC7Z010-1CLG400C استفاده می کنیم.

- Vivado Zybo را به عنوان یکی از تابلوهای از پیش تعریف شده خود ذکر نکرده است. را انتخاب کنید: "parts" سپس xc7z010clg400-1 را جستجو کنید.

- اگر قسمت اشتباهی را به اشتباه انتخاب کرده اید ، می توانید به راحتی تراشه ها را تغییر دهید: ابزارها -> تنظیمات پروژه -> عمومی و روی نقاط سمت راست "پروژه دستگاه" کلیک کنید

-

روی ایجاد طرح بلوک کلیک کنید.

فعلاً نام آن را design_1 بگذارید

- یک نوار سبز رنگ می بینید که می گوید Add IP ، روی آن کلیک کنید.

-

Zynq را جستجو کنید.

- روی ZYNQ7 Processing System دوبار کلیک کنید ،

- این بلوک در طراحی بلوک ما ظاهر می شود.

- یک نوار سبز رنگ می بینید که می گوید Run Block Automation ، روی آن کلیک کنید.

- zybo_zynq_def.xml را در زیر بارگیری کنید.

-

در Vivado ، روی "وارد کردن تنظیمات XPS" کلیک کنید و "zybo_zynq_def.xml" را انتخاب کنید.

این پیکربندی بلوک Vivado را با همه لوازم جانبی داخلی Zybo و تعیین پین ها پر می کند

-

روی بلوک ZYNQ دوبار کلیک کنید.

-

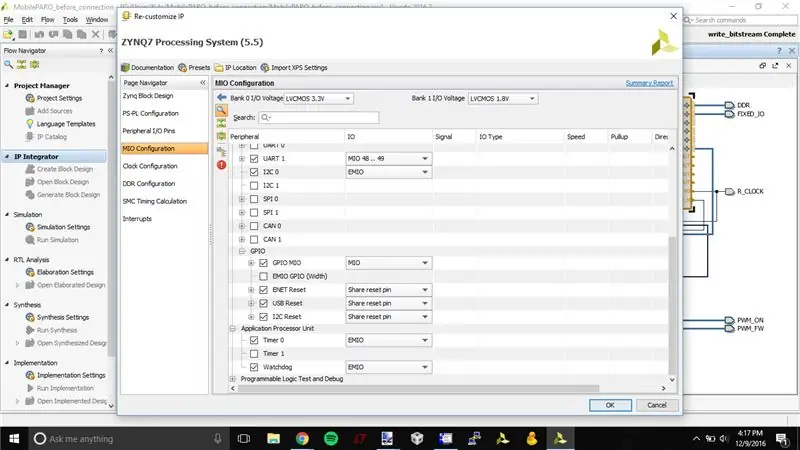

پیکربندی MIO

- فعال کردن تایمر 0 (تحت واحد پردازش برنامه - img 1)

- فعال کردن Watchdog (در بخش واحد پردازشگر برنامه 1)

- فعال کردن GPIO-> GPIO MIO (تحت واحد پردازشگر برنامه - img 2)

- GPIO-> ENET Reset را فعال کنید (در قسمت I/O Peripherals- img 2)

-

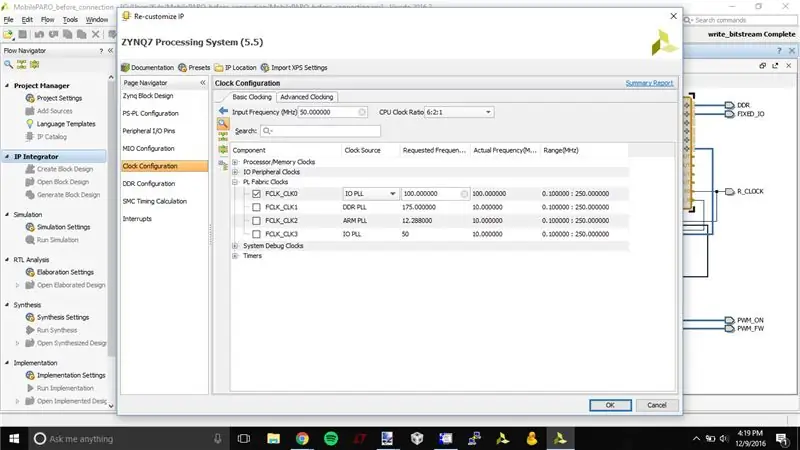

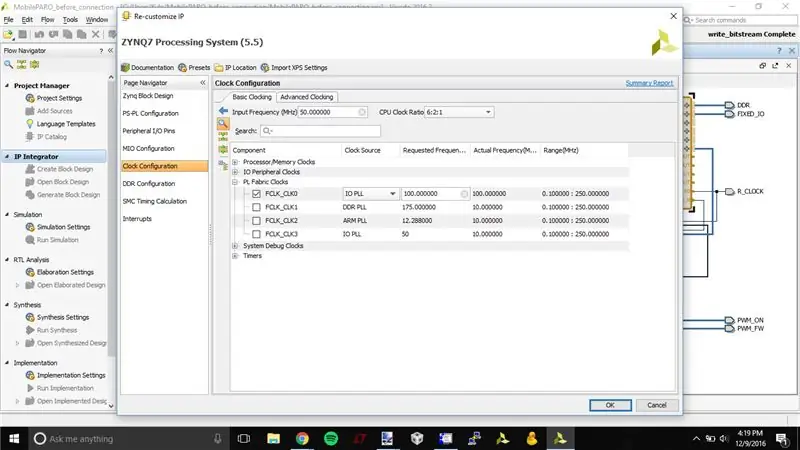

پیکربندی ساعت

FCLK0 را غیرفعال کنید (تحت PL Fabric Clocks - img 3)

-

- روی Ok کلیک کنید.

-

اکنون "Block Automation" را اجرا کنید.

س questionsالاتی در مورد سیگنال ها وجود دارد ، می گویند OK

-

روی "ایجاد HDL Wrapper" کلیک کنید.

ما می خواهیم بسته بندی ایجاد شده را کپی کنیم تا امکان ویرایش کاربر فراهم شود

- روی OK کلیک کنید.

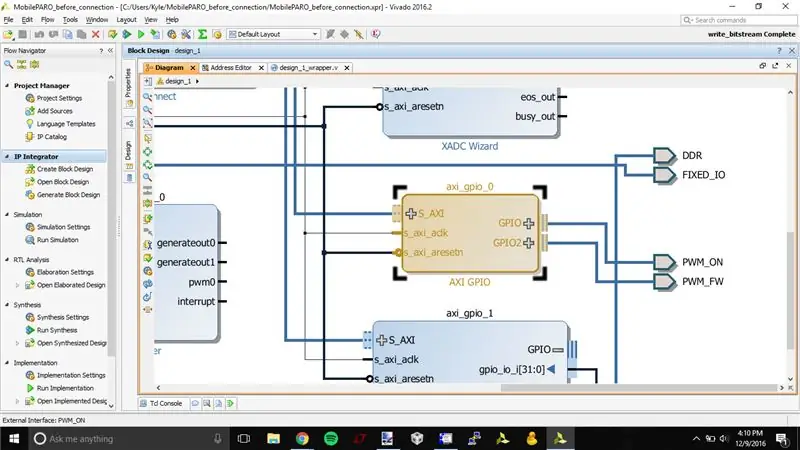

مرحله 2: ایجاد PWM ارنی در Vivado

این مرحله یک IP PWM با ورودی های ارسال شده از طریق کتابخانه AXI ایجاد می کند.

-

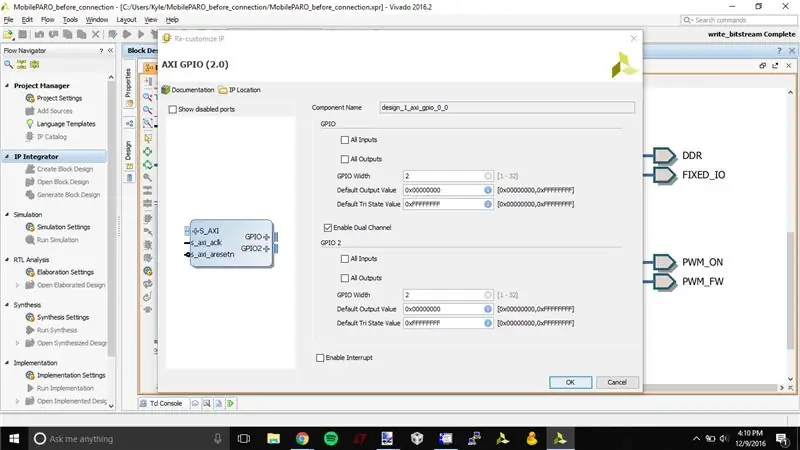

با راست کلیک روی پس زمینه و کلیک روی "افزودن IP" بلوک AXI GPIO ایجاد کنید

"AXI_GPIO" را در نوار جستجو تایپ کنید و این بسته را انتخاب کنید

-

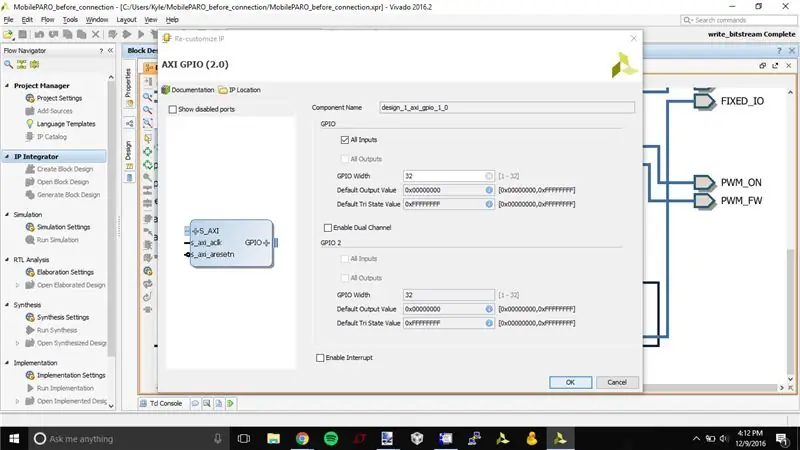

با دوبار کلیک روی بلوک axi_gpio_0 جدید ، IP را مجدداً سفارشی کنید

- تحت GPIO ، عرض GPIO را روی 2 تنظیم کنید. این بیت ها سیگنال PWM_ON برای هدایت هر نمونه ماژول PWM خواهند بود.

- روی "فعال کردن کانال دوگانه" کلیک کنید

- در GPIO 2 ، عرض GPIO را روی 2 تنظیم کنید. این بیت ها سیگنال PWM_FW برای تنظیم جهت هر نمونه ماژول PWM خواهند بود.

-

روی پورت خروجی axi_gpio_0 با برچسب GPIO راست کلیک کرده و "Make External" را انتخاب کنید

- روی خروجی جدید با برچسب GPIO کلیک کنید و به برگه "Properties" در نوار ابزار سمت چپ بروید و نام را به PWM_ON تغییر دهید

- روی خروجی جدید با برچسب GPIO2 کلیک کنید و به برگه "Properties" در نوار ابزار سمت چپ بروید و نام آن را به PWM_FW تغییر دهید.

-

گزینه Run Connection Automation را در بنر سبز بالای بلوک دیاگرام انتخاب کنید.

اگر پورت ها را به صورت دستی متصل می کنید ، ممکن است آدرس های AXI پیکربندی نشوند که بعداً منجر به مشکلات ارتباطی می شود

-

در پنجره ناوبر جریان ، مدیر پروژه -> افزودن منابع را برای ایجاد یک بلوک IP سفارشی جدید انتخاب کنید

- "افزودن یا ایجاد منابع طراحی" را انتخاب کرده و بعدی را بزنید

- روی "ایجاد فایل" کلیک کنید ، نوع فایل را به "SystemVerilog" تغییر دهید و "pwm" را در قسمت نام فایل تایپ کنید ، سپس روی OK کلیک کنید

- روی پایان کلیک کنید

-

پنجره Define Module را با فشار دادن OK نادیده بگیرید (بعداً این موارد را رونویسی می کنیم)

اگر می پرسد آیا مطمئن هستید ، روی Yes کلیک کنید

-

در برگه منابع ، روی pwm.sv (واقع در "منابع طراحی/design_1_wrapper") دوبار کلیک کنید

کل کد SystemVerilog را از فایل pwm.txt که در زیر ضمیمه شده است کپی/جایگذاری کنید

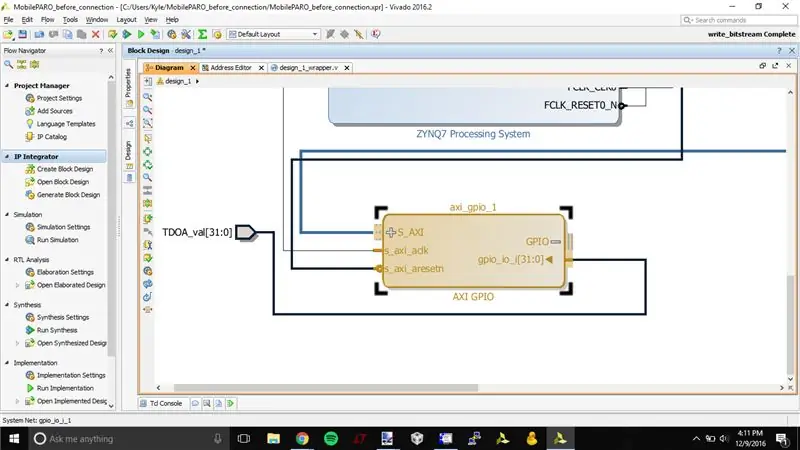

مرحله 3: ایجاد TDOA ارنی در Vivado

این مرحله یک IP TDOA ایجاد می کند که خروجی آن را می توان از طریق کتابخانه AXI خواند

-

با راست کلیک روی پس زمینه و کلیک روی "افزودن IP" ، بلوک AXI GPIO ایجاد کنید

"AXI_GPIO" را در نوار جستجو تایپ کنید و این بسته را انتخاب کنید

-

با دوبار کلیک روی بلوک جدید axi_gpio_1 ، IP را مجدداً سفارشی کنید

- در GPIO ، کادر "همه ورودی ها" را علامت زده و عرض GPIO را روی 32 تنظیم کنید. این گذرگاه تفاوت زمانی رسیدن بین دو سنسور را نشان می دهد.

- در داخل بلوک axi_gpio_1 ، روی + کنار درگاه GPIO کلیک کنید تا gpio_io_i [31: 0] نمایان شود.

-

روی پورت خروجی axi_gpio_1 با برچسب gpio_io_i [31: 0] راست کلیک کرده و "Make External" را انتخاب کنید

روی ورودی جدید با برچسب gpio_io_i [31: 0] کلیک کنید و به برگه "Properties" در نوار ابزار سمت چپ بروید و نام را به TDOA_val تغییر دهید

-

گزینه Run Connection Automation را در بنر سبز بالای بلوک دیاگرام انتخاب کنید.

در صورت اتصال دستی پورت ها ، آدرس های AXI ممکن است پیکربندی نشوند که بعداً منجر به مشکلات ارتباطی می شود

-

در پنجره ناوبر جریان ، مدیر پروژه -> افزودن منابع را برای ایجاد یک بلوک IP سفارشی جدید انتخاب کنید

- "افزودن یا ایجاد منابع طراحی" را انتخاب کرده و بعدی را بزنید

- روی "ایجاد فایل" کلیک کنید ، نوع فایل را به "SystemVerilog" تغییر دهید ، و "tdoa" را در قسمت نام فایل تایپ کنید ، سپس روی OK کلیک کنید

- روی پایان کلیک کنید

-

پنجره Define Module را با فشار دادن OK نادیده بگیرید (بعداً این موارد را رونویسی می کنیم)

اگر می پرسد آیا مطمئن هستید ، روی Yes کلیک کنید

-

در برگه منابع ، روی tdoa.sv (واقع در "منابع طراحی/design_1_wrapper") دوبار کلیک کنید

کل کد SystemVerilog را از فایل tdoa.txt که در زیر ضمیمه شده است کپی/جایگذاری کنید

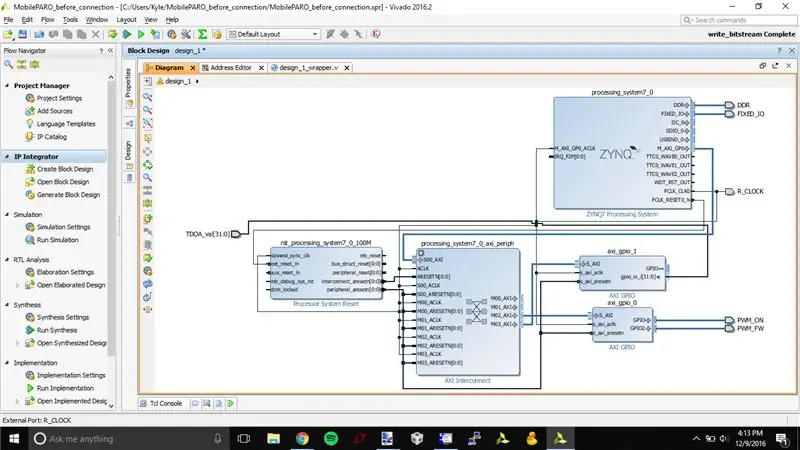

مرحله 4: بسته بندی و صادرات Ernie

- بررسی کنید که بلوک دیاگرام مانند تصویر پیوست شده به نظر برسد

-

در برگه منابع ، روی design_1.bd راست کلیک کرده و "Create HDL Wrapper …" را انتخاب کنید.

- "کپی خروجی ایجاد شده برای ویرایش کاربر" را انتخاب کنید ، سپس "OK" را فشار دهید

- کد را از design_1_wrapper.txt ضمیمه شده در زیر کپی کرده و به جای کد ایجاد شده طراحی_1_wrapper.v بچسبانید

- ذخیره طراحی_1_wrapper.v

-

در برگه منابع ، روی فایل ZYBO_Master.xdc در قسمت Constraints/constrs1 دوبار کلیک کنید

- کد را از ZYBO_Master.txt پیوست زیر کپی کرده و به جای کد موجود ZYBO_Master.xdc بچسبانید

-

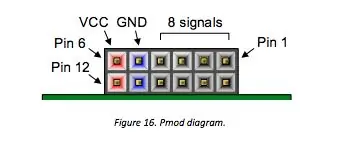

به پین های ورودی/خروجی زیر توجه کنید:

- L15: سیگنال PWM برای موتور سمت چپ (Pmod JA2 در Zybo)

- L14: سیگنال PWM برای موتور مناسب (Pmod JA8 در Zybo)

- V12: ورودی دروازه از سنسور صدا 1 (Pmod JE1 در Zybo)

- K16: ورودی دروازه از سنسور صدا 2 (Pmod JE2 در Zybo)

-

در پنجره ناوبر جریان ، روی "Generate Bitstream" در قسمت Program and Debug کلیک کنید

اگر فکر می کنید این کار بلافاصله انجام شده است ، احتمالاً اینطور نیست. جدی ، چای درست کن

-

روی File-> Export-> Generate Hardware کلیک کنید

گزینه "Include Bitstream" را علامت زده و OK را بزنید

- روی فایل-> راه اندازی SDK کلیک کنید

مرحله 5: ساختن ارنی

- سرووها را روی شاسی سروو نصب کنید.

-

پس از برگه داده سرویس ها ، موارد زیر را انجام دهید:

- زمین سرویس ها را به پین های زمینی در Zybo's JA Pmod متصل کنید (به تصویر pinout پیوست شده مراجعه کنید)

-

پین برق سروها را به باتری AA وصل کنید

ما دریافتیم که وقتی سرووها به Zybo's Vdd متصل می شوند ، برد بیش از حد جریان می یابد و باعث می شود که برد به طور مداوم بازنشانی شود

- پین های سیگنال ورودی را به پایه های خروجی مناسب Zybo وصل کنید (چپ: JA2 ، راست: JA8)

- سنسورهای صوتی را در قسمت جلوی شاسی ، رو به جلو نصب کنید و آنها را تا حد ممکن به هم نزدیک نگه دارید

-

از راهنمای اتصال سنسور صدا برای ادغام سنسورهای صدا استفاده کنید

- سیم و پایه های Vdd هر سنسور صدا را به زمین و پین های Vdd را روی JE Pmod Zybo سیم کشی کنید (به تصویر pinout پیوست شده مراجعه کنید)

- پین Gate سنسور صدا سمت چپ را به JE1 وصل کنید

- پین Gate سنسور صدا را به JE2 وصل کنید

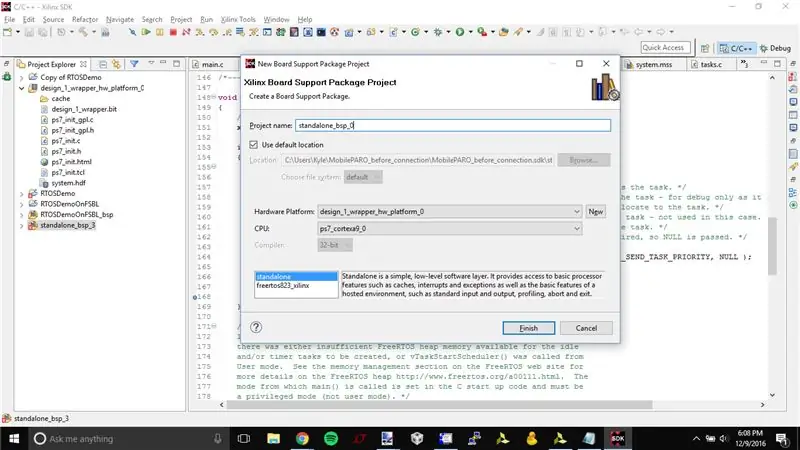

مرحله 6: اولین BSP ارنی

-

یک BSP ایجاد کنید تا پلتفرمی را که به تازگی ایجاد کرده ایم ، جمع بندی کنید.

می توانید این را از طریق فایل -> جدید -> بسته پشتیبانی پشتیبانی دریافت کنید

-

جادوگری ظاهر می شود که به شما در ایجاد BSP کمک می کند.

- ما می خواهیم این BSP را با پلتفرمی که اخیراً ایجاد کرده ایم گره بزنیم

- پلتفرم سخت افزاری باید با آنچه ما ایجاد کردیم مطابقت داشته باشد (تصویر 1 را ببینید)

- CPU ما CPU _0 خواهد بود.

- روی پایان کلیک کنید

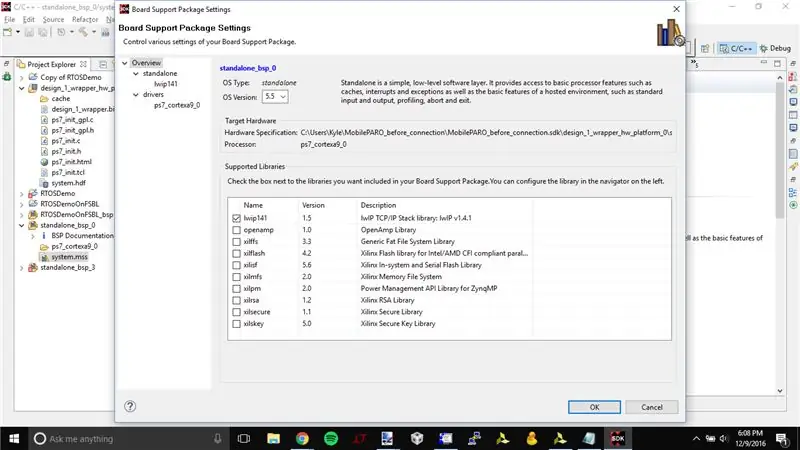

- مطمئن شوید که lwip141 را برای درج با bsp خود در پنجره باز شده علامت بزنید (تصویر 2 را ببینید)

مرحله 7: FreeRTOS'ing Ernie

-

آخرین نسخه FreeRTOS را از Sourceforge بارگیری کنید.

اگر بارگیری اجرایی است ، آن را اجرا کنید تا فایلهای FreeRTOS را در فهرست پروژه خود استخراج کنید

- آن SDK را باز نگه دارید و روی File -> Import کلیک کنید.

- ما می خواهیم روی General-> From an Existing Workspace کلیک کنیم و سپس می خواهیم به جایی که FreeRTOS را بارگیری کرده ایم برویم.

-

نسخه ی نمایشی ما در FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702 قرار دارد. با انتخاب این پوشه ، باید شاهد سه پروژه ظاهر شویم (کد ما (سیستم عامل) ، BSP و بستر HW).

فقط RTOSDemo را به فضای کاری فعلی خود وارد کنید

-

در همه پروژه های پوشه "آبی" BSP مرجع را تغییر دهید

- راست کلیک کرده و گزینه “Change Referenced BSP” را انتخاب کنید.

- BSP را که برای Zybo خود ایجاد کرده اید انتخاب کنید

- ویرایش کد در پوشه های SDK Blue Xilinx پروژه های کد واقعی هستند.

مرحله 8: وارد کردن کد C Ernie

- در فهرست RTOSDemo/src ، main.c موجود را با فایل main.c پیوست شده در اینجا بازنویسی کنید.

- فایل main_sound.c را در فهرست RTOSDemo/src کپی کنید.

مرحله 9: اشکال زدایی ارنی

- Run -> Debug Configurations را انتخاب کنید

- در پنجره سمت چپ ، یک اجرای سیستم اشکال زدایی جدید ایجاد کنید

-

در برگه تنظیمات هدف ،

"Reset Entire System" را انتخاب کنید تا هم آن و هم ps7_init انتخاب شوند

-

حالا برگه Application را انتخاب کنید.

- "بارگیری برنامه" را انتخاب کنید

- هسته cortexa9_0 را روی "توقف در ورود برنامه" تنظیم کنید

- روی Apply and Debug کلیک کنید.

- بررسی کنید که در فرآیند اشکال زدایی خطایی وجود ندارد

- با نگاهی دقیق به ربات ، دکمه Resume را فشار دهید تا برنامه بدون ضربه زدن به نقاط شکست اجرا شود

- ربات اکنون باید بچرخد و به سمت صداهای بلند حرکت کند. بله!

گام دهم: ایجاد خودمختاری ارنی

- هنگامی که پروژه شما آماده اجرا است (می توانید بدون اشکال از طریق اشکال زدایی اجرا کنید) آماده هستید تا آن را بر روی فلش مموری روی برد خود بارگذاری کنید.

-

پروژه ای را که "پروژه بارگذاری اولیه مرحله" (FSBL) نامیده می شود ایجاد کنید و شامل تمام دستورالعمل هایی است که برد شما برای بارگیری فایل های پروژه شما (جریان بیت و سیستم عامل) در هنگام راه اندازی نیاز دارد.

- را انتخاب کنید: فایل-> جدید-> برنامه پروژه و پنجره زیر ظاهر می شود.

- نام دلخواه خود را بگذارید (یعنی "FSBL")

- اطمینان حاصل کنید که بستر سخت افزاری همان چیزی است که با آن کار می کنید

- بعدی را فشار دهید (پایان را فشار ندهید)

- قالب Zynq FSBL را انتخاب کنید

- روی پایان کلیک کنید.

- پس از تکمیل فرآیند ایجاد ، در صورت مشاهده دو پوشه جدید زیر در پنجره Project Explorer ، می دانید که آیا همه چیز کار کرده است یا خیر.

-

ایجاد یک تصویر بوت در حال حاضر شما باید تصویر بوت را ایجاد کنید.

- روی پوشه پروژه خود راست کلیک کنید (در این مورد فایل من "RTOSDemo" نامیده می شود)

- از منوی کشویی روی "ایجاد تصویر بوت" کلیک کنید

-

اگر همه چیز به درستی پیوند خورده باشد ، پروژه می داند که به چه فایل هایی نیاز دارد و پنجره زیر همانطور که در زیر می بینید ظاهر می شود (مهم این است که شما دارای 3 پارتیشن در قسمت Boot image ، bootloader ، فایل بیت خود و فایل.elf پروژه های خود هستید.)

اگر اینطور نیست احتمالاً مشکلی در پیوند پروژه شما وجود دارد. اطمینان حاصل کنید که پوشه های پروژه به BSP های مربوطه متصل شده اند

- روی دکمه "ایجاد تصویر" کلیک کنید

-

آخرین مرحله برای انجام نرم افزار این است که اکنون تصویر قبلی خود را در حافظه برد فلش کنید

- از نوار ابزار اصلی SDK ، Xilinx Tools-> Program Flash Memory را انتخاب کنید

- اطمینان حاصل کنید که بستر سخت افزاری صحیح انتخاب شده است و مسیر فایل تصویر به درستی به فایل. BIN ایجاد شده در مرحله قبل اشاره می کند.

- "qspi single" را از نوع فلش انتخاب کنید

- علامت "تأیید بعد از فلاش" را بزنید تا یکپارچگی را تضمین کنید اما نیازی به آن نیست

- پیکربندی برد خود در نهایت باید اطمینان حاصل کنید که حالت برنامه نویسی بردها (JP5) به درستی تنظیم شده است که هنگام راه اندازی BootROM از qspi (که شامل مواردی است که به تازگی فلش کرده اید) بوت شود.

- اکنون به سادگی دستگاه را چرخه بزنید و مطمئن شوید "Logic Configuration Done LED" (LED 10) سبز روشن است.

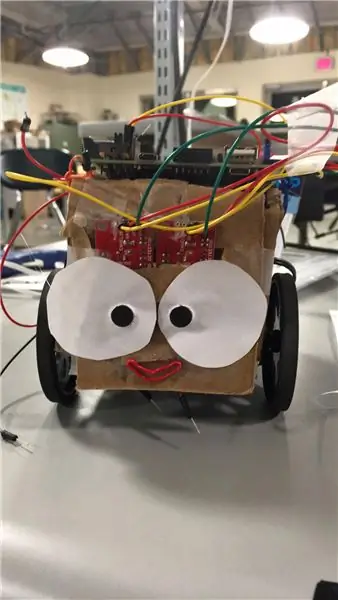

مرحله 11: ساختن ارنی ناز

- خز

- خز زیاد

- چشم های بزرگ!

- … کلاه بالایی

توصیه شده:

طرز تهیه مکعب LED - مکعب LED 4x4x4: 3 مرحله

طرز تهیه مکعب LED | LED Cube 4x4x4: یک LED Cube را می توان یک صفحه LED دانست که در آن LED های ساده 5 میلی متری نقش پیکسل های دیجیتال را ایفا می کنند. یک مکعب LED به ما اجازه می دهد تا با استفاده از مفهوم یک پدیده نوری معروف به ماندگاری بینایی (POV) تصاویر و الگوهایی ایجاد کنیم. بنابراین،

اسباب بازی دایناسور Chrome با کنترل ژست دستی / طرز تهیه این / #خلاقیت هوشمند: 14 مرحله

اسباب بازی دایناسور Chrome کنترل شده با دست / چگونه می توان این کار را انجام داد / #خلاقیت: سلام دوستان ، در این آموزش من قصد دارم یک پروژه بسیار منحصر به فرد را به شما نشان دهم. بنابراین ، امروز من به شما نحوه کنترل بازی دایناسور کروم با حرکت دست خود را نشان خواهم داد. خیلی راحت اگر از این فناوری برای کنترل کروم DINO استفاده کنید ، سقوط خواهید کرد

طرز تهیه خانه آناناس باب اسفنجی: 12 مرحله

چگونه یک خانه آناناسی باب اسفنجی بسازیم: چه کسانی در آناناس زیر دریا زندگی می کنند؟ پاسخ این س (ال (باب اسفنجی) امروزه برای اکثر مردم کاملاً واضح است. تیم ما وظیفه طراحی و ساخت یک تکیه گاه برای تولید نمایشنامه آینده را بر عهده داشت. ایده ای که بلافاصله به وجود آمد

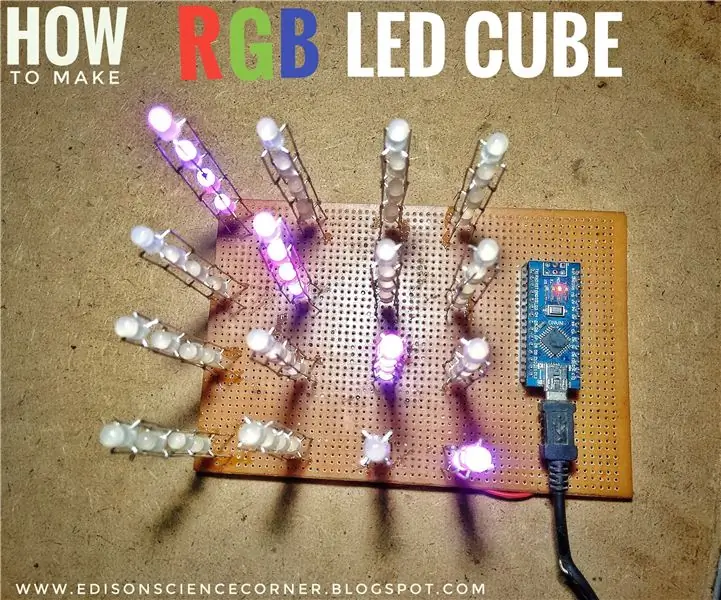

طرز تهیه مکعب LED Rgb: 5 مرحله

چگونه می توان Rgb Led Cube درست کرد: در این قسمت آموزشی من قصد دارم یک rgb led cube (مکعب شارلیپلکس) درست کنم … مکعب شارلیپلکس چیست …؟ Charlieplexing یک تکنیک برای رانندگی یک صفحه نمایش چندگانه است که در آن نسبتاً I/ پین O روی میکروکنترلر استفاده می شود ، به عنوان مثال برای رانندگی یک

طرز تهیه زنبور عسل: 6 مرحله

چگونه می توان زنبور وزوز را درست کرد: در اینجا راهی آسان و سرگرم کننده برای تهیه زنبور وزوز آمده است. دارای موتور ارتعاشی در قسمت پایینی است که باعث می شود زنبور وزوز بزند و حرکت کند. انجام این کار با بچه های کوچکتر (5-7) یا اجازه دادن به بچه های بزرگتر (8 سال به بالا) با نظارت کمتری آسان است. روشن را آموزش می دهد