فهرست مطالب:

- تدارکات

- مرحله 1: الزامات پورت سریال

- مرحله 2: الزامات برنامه نویسی PIC

- مرحله 3: مشخصات JDM

- مرحله 4: شرح مدار

- مرحله 5: برای شبیه سازی آماده شوید

- مرحله 6: تغییرات ICSP

- مرحله 7: نتایج شبیه سازی

- مرحله 8: نتیجه گیری

- مرحله نهم: و در نهایت

تصویری: مرور برنامه نویس JDM: 9 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:52

JDM یک برنامه نویس محبوب PIC است زیرا از پورت سریال ، حداقل اجزاء و نیاز به منبع تغذیه استفاده نمی کند. اما سردرگمی وجود دارد ، با بسیاری از تغییرات برنامه نویس در شبکه ، کدام یک با کدام PIC کار می کند؟ در این "قابل آموزش" ما JDM را آزمایش کردیم و من نحوه شبیه سازی مدار با استفاده از Spice را نشان می دهم که به همه سوالات شما پاسخ می دهد!

تدارکات

LTspice را می توانید از دستگاه های آنالوگ در اینجا بارگیری کنید.

شما همچنین به فایلهای مدار JDM در اینجا نیاز دارید.

مرحله 1: الزامات پورت سریال

JDM نیاز به یک پورت سریال دارد که با مشخصات EIA232 مطابقت دارد ، در حالت ایده آل با سطوح ولتاژ +12/-12.

با توجه به برگه اطلاعات Texas Instruments Line Driver MC1488 (شکل 3)

امپدانس خروجی = 4V/8mA = 500 اهم

محدودیت جریان اتصال کوتاه = 12 میلی ولت ، بدون محدودیت زمانی - بدون آسیب به تراشه.

امپدانس ورودی گیرنده خط = 3k تا 7k اهم توصیه می شود.

پورت های سری در رایانه های رومیزی قدیمی از +12v/-12V استفاده می کنند که این نیاز را برآورده می کند.

پورت های سری در رایانه های شخصی جدیدتر از ولتاژهای پایین استفاده می کنند. JDM ممکن است کار کند یا نکند - پاسخ پیچیده تر است.

مرحله 2: الزامات برنامه نویسی PIC

اطلاعات مربوط به الزامات برنامه نویسی PIC از Microchip به دست آمده است. موارد فوق برای یک دستگاه معمولی است.

مرحله 3: مشخصات JDM

آیا وب سایت اصلی JDM در مه زمان گم شده است؟ این باعث می شود حدس بزنیم که ابتدا طراح برای این مشخصات در نظر گرفته است.

- ارائه VDD = 5V ، و حداکثر تا IDD = 2mA (برای نسخه "در سوکت")

- VHH = 13V و حداکثر تا IHH = 0.2mA ارائه دهید.

- MCLR زمان افزایش tVHHR = حداکثر 1uS

- نسخه ICSP باید بتواند MCLR را در برابر 22k pull-up روی هدف پایین بکشد.

مرحله 4: شرح مدار

شکل JDM1 بر اساس مدار استاندارد JDM برگرفته از وب سایت PICPgm است. این برنامه نویس "PIC in Socket" است که PIC از پین های TX و RTS نیرو می گیرد. درک نمودار اصلی دشوار بود ، بنابراین من آن را با استفاده از روش عادی جریان از بالا به پایین ترسیم کرده ام. و نشانگرهای LED "RESET" ، "PROG" و "RTS" را که در هنگام ساخت و آزمایش لازم است اضافه کرده ام. امیدوارم اینها هیچ تاثیری بر رفتار نداشته باشند.

قرارداد معمول طراحی مدار در همه زمینه ها مشترک است ، اما ویژگی اصلی JDM این است که زمین پورت سریال (GND) به VDD متصل است. این امر باعث ایجاد سردرگمی می شود زیرا سیگنال های پورت سریال با توجه به GND ، سیگنال های PIC با توجه به زمین منطقی (VSS) اندازه گیری می شود.

هنگامی که TX بالا می رود ، Q1 به عنوان دو دیود جانبدار جلو رفتار می کند. (گردآورنده Q1 مانند عملکرد ترانزیستور معمولی تعصب ندارد). کلکتور Q1 شارژ C2 می کند که توسط Zener (D3) در VDD+8V بسته می شود. امیتر Q1 13V را به MCLR برای حالت برنامه/تأیید می رساند.

وقتی TX پایین می آید ، خازن C3 از طریق D1 شارژ می شود و VSS توسط Zener (D5) در VDD-5V بسته می شود. همچنین TX در (VSS-0.6) توسط D1 محکم شده است. Q1 خاموش است ، C1 شارژ خود را برای نبض برنامه نویسی بعدی نگه می دارد. MCLR در 0V توسط D2 بسته شده است ، بنابراین PIC در حال حاضر بازنشانی شده است.

وقتی RTS زیاد است ، ساعت به PGC منتقل می شود. گیره D4 PGC در منطق VDD بالا است. هنگامی که RTS کم است ، خازن C3 از طریق D6 شارژ می شود و VSS توسط Zener (D5) در VDD-5V بسته می شود. D6 PGC را در VSS یا منطق 0 محکم می کند.

در طول برنامه نویسی ، داده های ارسال شده در DTR در PGD خوانده می شود ، که PIC آنها را به عنوان ورودی پیکربندی می کند. هنگامی که DTR زیاد است ، Q2 به عنوان "دنبال کننده امیتر" عمل می کند و ولتاژ PGD تقریباً (VDD-0.6) یا منطق 1 است. هنگامی که DTR کم است ، Q2 به عنوان یک ترانزیستور بد عمل می کند (پین های ساطع کننده و جمع کننده معکوس هستند). Q2 PGD را پایین می آورد ، که توسط D7 در VSS یا منطق 0 بسته می شود.

در حین تأیید ، PIC PGD را به عنوان خروجی برای ارسال داده به پورت سریال پیکربندی می کند. DTR باید بالا باشد و داده ها در CTS خوانده شوند. هنگامی که خروجی PGD زیاد است ، Q2 خاموش است ، CTS = DTR = +12V. هنگامی که خروجی PGD کم است ، Q2 روشن است. جمع کننده Q2 جریان (12V+5V)/(1k+1k5) = 7mA را از DTR می کشد و CTS را پایین می کشد ، به VSS.

مرحله 5: برای شبیه سازی آماده شوید

ادویه LT را بارگیری کنید ، فایلهای مدار (*.asc) ارائه شده در اینجا را ذخیره و باز کنید. برای شبیه سازی مدار ، باید مقداری ورودی به آن بدهیم ، سپس خروجی ها را "ردیابی" کنیم. V1 ، V2 V3 پورت سریال 12V را با امپدانس خروجی R11 ، R12 ، R13 شبیه سازی می کند.

- V1 2 تپ برنامه در TX از 0.5 میلی ثانیه تا 4.5 میلی ثانیه تولید می کند

- V2 انفجار پالس های داده را در DTR از 1.5 تا 4.5 میلی ثانیه ایجاد می کند

- V3 انفجار پالس ساعت را در RTS از 0.5 تا 3.5 میلی ثانیه ایجاد می کند

اجزای V4 ، X1 ، R15 و R16 همه بخشی از شبیه سازی هستند.

- V4 برای تأیید داده ها 2 پالس از 2.5 تا 4.5 میلی ثانیه تولید می کند.

- Jumper X1 OUTPUT را در PGD شبیه سازی می کند.

- R15 ، R16 "بارگیری" PIC را در VDD و MCLR شبیه سازی می کند.

مرحله 6: تغییرات ICSP

شکل JDM3 نسخه برنامه نویسی "در مدار" را نشان می دهد. تغییرات از نسخه اصلی هستند

- سوکت ZIF را با اتصال ICSP جایگزین کنید.

- PIC اکنون از منبع تغذیه به مدار مورد نظر (V5) تغذیه می کند.

- زنر 5 ولت (D5) را بردارید.

- خازن کوچک 100pF (C4) در کنار PIC در مدار مورد نظر منتقل می شود.

- LED ها در صورت امکان از برد مدار تغذیه می کنند.

- مقاومت کششی MCLR (R10) و دیود (D10) در مدار مورد نیاز است.

- هشدار تخته هدف باید دارای منبع "شناور" باشد ، در حالت ایده آل یک باتری.

- همزمان با JDM ، زمین هدف (VSS) را به زمین رایانه/رایانه وصل نکنید.

پس از شبیه سازی JDM1 ، مشکل زمان طولانی شارژ روی C2 آشکار شد. سپس پس از خواندن Fruttenboel به نظر می رسد که C2 و Q1 به عنوان اصلاحیه اصلی اضافه شده اند. من نمی توانم فکر کنم که C2 و Q1 جدا از ایجاد مشکل در نظر دارند چه کاری انجام دهند. بنابراین برای JDM4 ، ما به طرح قدیمی Fruttenboel باز می گردیم که درک آن ساده و ساده است. D1 و D3/LED2 بستن MCLR بین VSS و VDD+8V. مقدار R1 به 3k3 کاهش می یابد ، فقط برای روشن شدن LED2 در 12V کافی است.

JDM4 همچنین برای کار با پورت های سریال ضعیف تر طراحی شده است. هنگامی که TX بالا می رود (+9V) ، منبع جریان TX = (9-8)/(1k +3k3) = 0.2ma ، فقط به اندازه کافی برای کشیدن MCLR بالا هر چند برای روشن کردن LED2 کافی نیست. هنگامی که TX پایین می رود (حدود -7V) ، سینک جریان TX = (9-7)/1k = 2mA. جریان LED1 = (7-2 برای led)/(2k7) = 1.8mA. MCLR جریان پایین = 7-5.5/3k3 = 0.5mA.

این مدار نیز مورد آزمایش قرار گرفته است (شبیه سازی JDM5) تا ببینیم در مورد پورت های سریال +/- حداقل 7 ولت ، که در آن ولتاژ کافی برای حفظ VHH = 13V وجود ندارد ، چه اتفاقی می افتد. هدف C1 اکنون آشکار می شود ، C1 باعث افزایش کوتاه مدت +ve در MCLR می شود ، یک جهش 33us در لبه رو به بالا TX ، به اندازه کافی طولانی برای PIC برای ورود به حالت برنامه نویسی ، شاید؟ اما بلوز X2 (LED1 را غیرفعال کنید) بردارید زیرا جریان کافی برای پایین آوردن MCLR و روشن کردن LED1 با هم وجود ندارد. وقتی TX پایین می رود ، سینک جریان TX = (7V-5.5V)/(1k+3k3) = 0.3mA ، فقط کافی است تا MCLR را در برابر R10 کششی پایین بکشد.

مرحله 7: نتایج شبیه سازی

برای مشاهده فایل های گرافیکی ، بهتر است روی پیوندهای زیر راست کلیک کرده ، سپس "باز کردن پیوند در برگه جدید" را انتخاب کنید.

شبیه سازی 1: اثری از MCLR ، VSS و RTS برای JDM1 اصلی. مشاهده فوری 1 ، 2 و 3 آشکار است.

شبیه سازی 2: ردیابی MCLR و VSS و RTS برای اصلاح JDM2 ، که مشکلات قبلی را برطرف می کند.

شبیه سازی 3: ردیابی PGD ، VSS و PGC برای ارسال داده در JDM2 در حالت برنامه. مشاهده 4 در 3.5mS.

شبیه سازی 4: ردیابی PGD ، VSS و CTS برای JDM2 در حالت تأیید (بلوز X1 درج شده است). خوب

شبیه سازی 5: اثری از MCLR ، VSS ، PGD و PGC برای JDM3. ICSP با استفاده از برق از مدار مشکلات زیادی را حل می کند.

شبیه سازی 6: ردیابی MCLR ، VSS ، PGD و PGC برای JDM4 با پورت سریال +/- 9V. MCLR بلافاصله بالا می رود ، به طور کامل کار می کند.

شبیه سازی 7: اثری از MCLR ، VSS و TX برای JDM5 با پورت سریال +/- 7V و بلوز X2 حذف شده است. C1 باعث افزایش +ve (افزایش) در لبه بالایی MCLR می شود ، تقریباً برای فشار دادن MCLR بالاتر از TX به 13V.

مرحله 8: نتیجه گیری

اسپایس در فاش کردن "اسرار پنهان" عملکرد مدار واقعاً خوب است. بدیهی است که مدار JDM کار می کند و با بسیاری از تراشه های PIC سازگار است ، اما مشاهدات زیر محدودیت های احتمالی/مشکلات سازگاری/خطاها را نشان می دهد؟

- زمان افزایش طولانی MCLR در حالی که C2 در اولین پالس TX به VPP شارژ می شود. مشخصات ناموفق 3

- هنگامی که TX بالا می رود و RTS پایین می رود ، پورت سریال C2 را شارژ می کند. اما RTS وظیفه شارژ C3 را نیز بر عهده دارد. هنگامی که هر دو به طور همزمان اتفاق می افتند ، بار بیشتری روی RTS ایجاد می شود ، در نتیجه C3 در شبیه سازی 2 میلی ثانیه بار را از دست می دهد (VSS افزایش می یابد). مشخصات ناموفق است 1.

- C3 پس از توقف پالس های ساعت در 3.5 میلی ثانیه ، بار خود را از دست می دهد (VSS شروع به افزایش می کند).

- هدف C2 چیست ، اصلا لازم است؟

راه حل ها

- احتمالاً PICPgm از یک نرم افزار "دور کار" استفاده می کند. آیا باید یک پالس TX طولانی برای پیش شارژ C2 اعمال کند ، سپس فقط بعد از پالس دوم TX وارد حالت برنامه نویسی شوید؟ برای شبیه سازی ، مقدار C2 را به 1uF کاهش داده و زمان افزایش 1 میلی ثانیه را نشان می دهد. یک راه حل ایده آل نیست.

- C2 و C3 را جدا کرده تا مستقل شارژ شوند. یک تغییر کوچک در JDM2 ، C2 به جای VSS به GND ارجاع داده می شود.

- حل شده توسط JDM3. ICSP بسیار مطمئن تر است زیرا PIC از مدار هدف تغذیه می کند.

- JDM4 مشکل 1 را حل می کند. این یک طرح ساده است که C2 را به کلی حذف می کند.

مرحله نهم: و در نهایت

اثبات پودینگ در خوردن است. این JDM کار می کند بنابراین استفاده از آن را ادامه دهید.

و توصیه های من عبارتند از:

- از JDM2 برای برنامه نویسی سوکت و پورت های سریال 12V استفاده کنید ،

- استفاده از JDM4 برای برنامه نویس ICSP و پورت های سریال بالاتر از +/- 9V ،

- از JDM4 با بلوز X2 حذف شده برای پورت های سریال بالاتر از +/- 7V استفاده کنید.

منابع:

ادویه آنالوگ دستگاه LT

picpgm

Fruttenboel

پروژه های PIC بیشتری را در sly-corner دنبال کنید

توصیه شده:

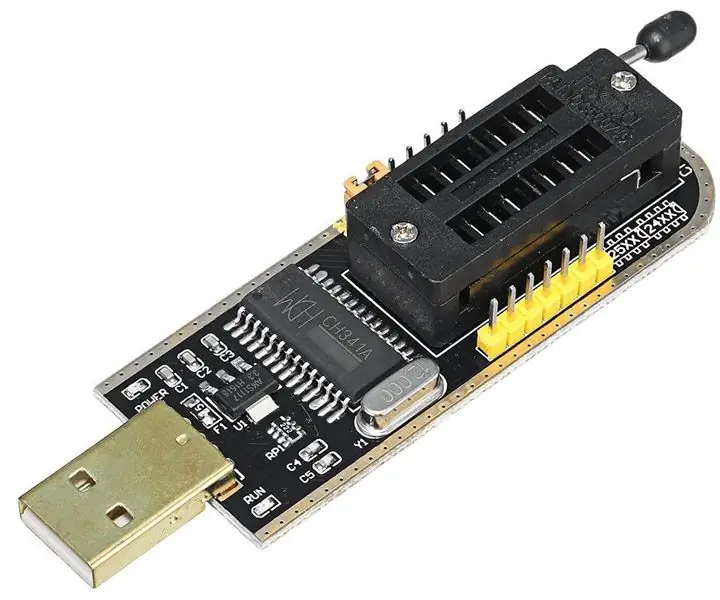

CH341A برنامه نویس: 8 مرحله

برنامه نویس CH341A: من اخیراً یک برنامه نویس مینی CH341A خریدم. مینی برنامه نویس سالم است و می تواند برای برنامه ریزی تراشه های سری 24 و 24 استفاده شود. این بسیار کم هزینه است ، اما بسیار مفید است زیرا می توانم از آن برای فلش BIOS کامپیوتر و سیستم عامل روتر خود استفاده کنم. WCH نسخه های مهربانی دارد

برنامه نویسی میکروکنترلرها با برنامه نویس USBasp در Atmel Studio: 7 مرحله

برنامه نویسی میکروکنترلرها با یک برنامه نویس USBasp در Atmel Studio: سلام من آموزش های زیادی را در مورد نحوه استفاده از برنامه نویس USBasp با Arduino IDE خواندم و آموختم ، اما برای تکالیف دانشگاه نیاز به استفاده از Atmel Studio داشتم و هیچ آموزشی پیدا نکردم. پس از تحقیق و مطالعه از طریق بسیاری از

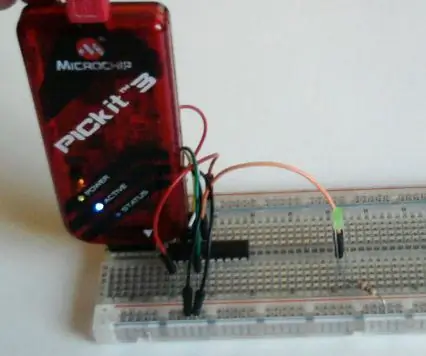

نحوه برنامه ریزی PIC MCU با برنامه نویس PICkit با استفاده از Breadboard: 3 مرحله

نحوه برنامه ریزی PIC MCU با برنامه نویس PICkit با استفاده از Breadboard: برای بازی با میکروکنترلرهای PIC (یا هر دستگاه دیگر) نیازی به ابزارهای گران قیمت و پیچیده ندارید. تنها چیزی که نیاز دارید یک تخته نان است که در آن مدار و برنامه نویسی خود را آزمایش کنید. البته نوعی برنامه نویس و IDE ضروری است. در این دستورالعمل

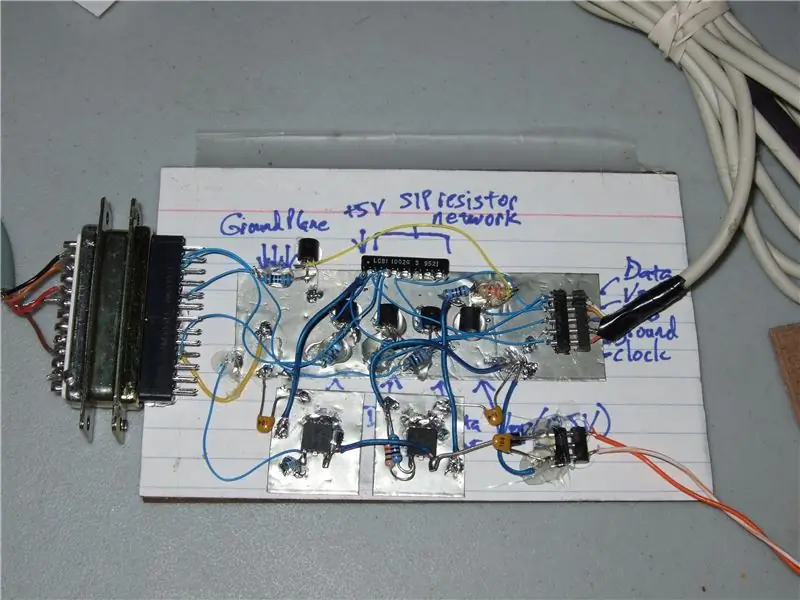

5 برنامه نویس ترانزیستور PIC *شماتیک به مرحله 9 اضافه شد: 9 مرحله

5 برنامه نویس PAN Transistor *شماتیک به مرحله 9 اضافه شد: برنامه نویس PIC خود را برای پورت موازی کامپیوتر خود بسازید. این تنوع در طراحی کلاسیک دیوید تایت است. بسیار قابل اعتماد است و نرم افزارهای برنامه نویسی خوبی به صورت رایگان در دسترس است. من برنامه نویس IC-Prog و PICpgm را دوست دارم. از همه بهتر این است که

Pic 16F676 ICSP سوکت برنامه نویسی برای برنامه نویس PICkit 2: 6 مرحله

عکس 16F676 ICSP سوکت برنامه نویسی برای برنامه نویس PICkit 2: من سعی می کنم این ماژول موتور DC دوگانه را برای پروژه ربات خود بسازم و فضا برای قرار دادن هدر پین ICSP روی PCB نداشتم. بنابراین من به سرعت این طرح را مسخره کردم