فهرست مطالب:

- مرحله 1: مرحله سوگیری مجدد

- مرحله 2: مقاومت سنجش جریان

- مرحله 3: تقویت کننده انتقال رسانایی

- مرحله 4: تقویت کننده ابزار دقیق

- مرحله 5: مرحله ورودی و کالیبراسیون

- مرحله 6: موارد پیشرفته: نشت طیفی (DC)

- مرحله 7: موارد پیشرفته: نشت طیفی (AC)

- مرحله 8: موارد پیشرفته: فاکتور سود نظری

- مرحله 9: موارد پیشرفته: PA Shift

تصویری: تجزیه و تحلیل امپدانس زیستی (BIA) با مراحل AD5933: 9

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:55

من علاقه مند به ساختن یک تجزیه و تحلیل امپدانس زیستی برای اندازه گیری ترکیبات بدن بوده ام و جستجوهای تصادفی من مدام از کلاس ابزار دقیق پزشکی 2015 در دانشگاه وندربیلت استفاده می کردم. من روی طراحی کار کرده ام و آن را کمی بهبود بخشیده ام. مایلم یافته های خود را با شما در میان بگذارم. اگر چیزی واضح نیست می توانید از این "راهپیمایی" استفاده کنید ، لطفاً بهبودها را پیشنهاد دهید. ممکن است روزی افکار خود را به شکل منسجم تری بنویسم ، اما در حال حاضر امیدوارم بتوانید از هر آنچه در اینجا می بینید استفاده کنید. (اگر فکر می کنید می توانید این را بنویسید و پیشرفت کنید ، خوش آمدید)

تدی

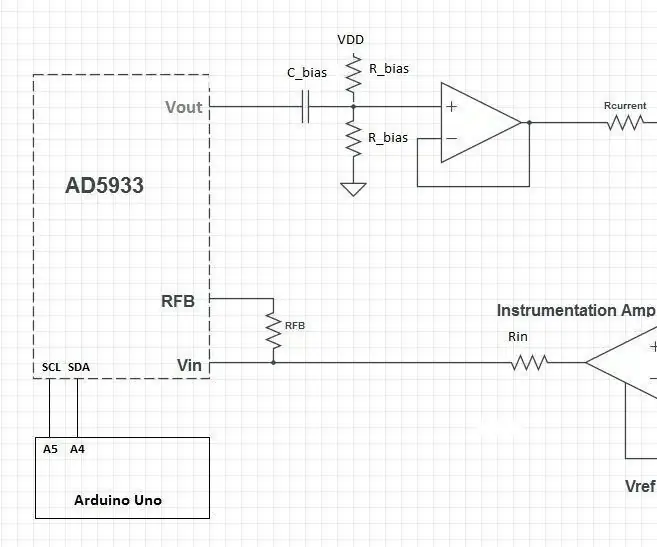

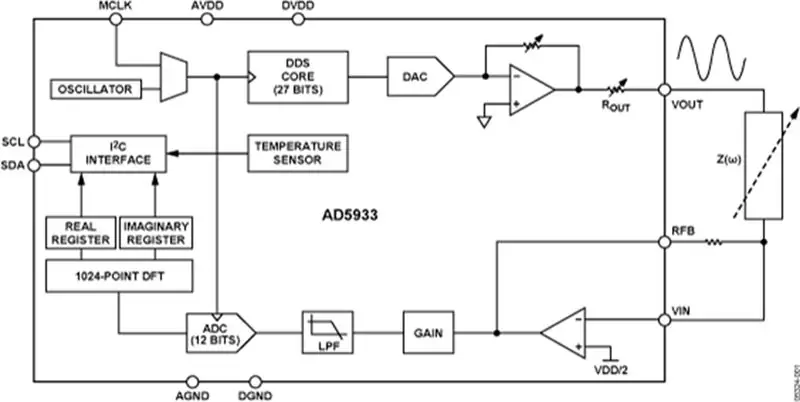

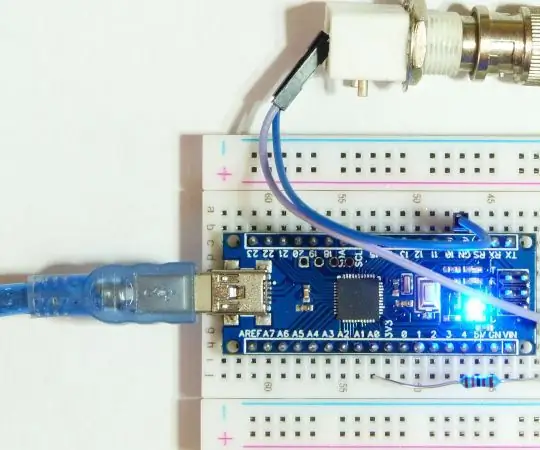

این طرح شامل تراشه AD5933 و یک قسمت جلویی آنالوگ سفارشی (AFE) برای اتصال AD5933 با بدنه است. سپس AD5933 اندازه گیری را انجام می دهد و نتایج را می توان توسط میکروکنترلر (به عنوان مثال آردوینو) پردازش کرد.

اگر قصد دارید از Arduino به عنوان منبع تغذیه استفاده کنید ، مطمئن شوید که تقویت کننده های عملیاتی و ابزار دقیق (op-amps و in-amps) از ولتاژهای به اصطلاح "منبع تغذیه تک" پشتیبانی می کنند و دارای مشخصات راه آهن به راه آهن هستند.

(در ادامه از منبع تغذیه (از آردوینو) 5 ولت و تنظیم محدوده 1 در AD5933 استفاده خواهم کرد.)

مرحله 1: مرحله سوگیری مجدد

قسمت اول AFE مرحله سوگیری مجدد است. سیگنال ولتاژ خروجی در وسط محدوده ولتاژ منبع تغذیه (VDD/2) متمرکز نیست. این با استفاده از یک خازن برای مسدود کردن قسمت DC سیگنال و ارسال آن از طریق یک تقسیم کننده ولتاژ برای اضافه کردن یک افست DC به سیگنال ، اصلاح می شود.

دو مقاومت جانبدار مجدد تا زمانی که یکسان باشند می توانند هر ارزشی داشته باشند. مقدار خاص پس از سقف نیز مهم نیست.

مرحله بایاس مجدد مانند یک فیلتر با گذر بالا عمل می کند و بنابراین دارای فرکانس قطع است:

f_c = 1 / (2 * pi * (0.5 * R) * C)

اطمینان حاصل کنید که فرکانس قطع چند دهه زیر حداقل فرکانسی است که برای استفاده از آن برنامه ریزی کرده اید. اگر قصد دارید از 1 کیلوهرتز در برنامه خود استفاده کنید ، باید به سراغ مقادیر محدوده و مقاومت بروید که فرکانس قطع را به ترتیب 1 تا 10 هرتز به شما می دهد.

آخرین قسمت این مرحله یک op-amp است که به عنوان دنبال کننده ولتاژ تنظیم شده است. این امر برای اطمینان از عدم تداخل مقادیر مقاومت در مرحله بعدی است

مرحله 2: مقاومت سنجش جریان

اولین قسمت مرحله بعدی مقاومت سنجش فعلی است. جریان از طریق این مقاومت همان جریانی است که تقویت کننده سعی می کند از طریق بدن آن را حفظ کند. مطمئن شوید که جریان مطابق با استانداردهای ایمنی IEC6060-1* باشد:

در زیر فرکانسهای 1 کیلوهرتز حداکثر 10 میکرو آمپر (RMS) از طریق بدن مجاز است. در فرکانسهای بالاتر از 1 کیلوهرتز معادله زیر حداکثر جریان مجاز را می دهد:

حداکثر جریان AC <(حداقل فرکانس در کیلوهرتز) * 10 میکرو آمپر (RMS)

رابطه بین حداکثر دامنه سیگنال AC و مقدار RMS آن عبارت است از: Peak = sqrt (2) * RMS. (10 میکرو آمپر RMS مربوط به 14 میکرو آمپر دامنه حداکثر)

با استفاده از قانون اهم بر روی مقاومت می توانیم مقدار مقاومت را مطابق با استاندارد ایمنی محاسبه کنیم. ما از ولتاژ تحریک AD5933 و حداکثر مقدار فعلی استفاده می کنیم:

U = R * I => R = U / I

به عنوان مثال. با استفاده از تنظیمات محدوده 1 Upeak = 3V / 2 = 1.5V (یا 1V @3.3V)

با استفاده از مقدار اوج 14 microAmp از بالا ، مقدار مقاومت حداقل 107 کیلو اهم را دریافت می کنم

منابع:

* دستگاههای آنالوگ: "طراحی مدار امپدانس زیستی برای سیستمهای فرسوده بدن"

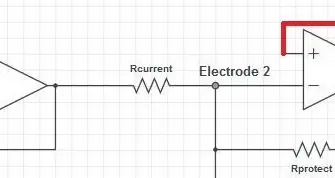

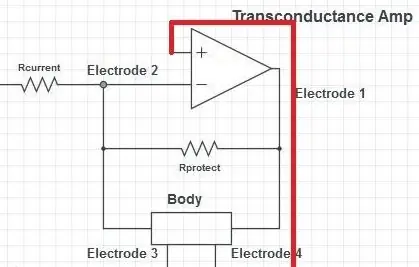

مرحله 3: تقویت کننده انتقال رسانایی

پس از مقاومت سنجش فعلی ، یک op-amp با پیکربندی بازخورد منفی وجود دارد. این به اصطلاح راه اندازی Load-in-the-Loop است. پایانه ورودی مثبت op-amp به ولتاژ VDD/2 متصل است. اکنون op-amp سعی می کند خروجی خود را در جهت مخالف سیگنال تحریک تنظیم کند به طوری که ولتاژ در ترمینال منفی برابر VDD/2 باشد. این امر باعث ایجاد نیروی بالقوه ای برای فشار دادن و کشیدن جریان از طریق بدن می شود.

جریان خروجی از ترمینال منفی op-amp عملا صفر است. بنابراین تمام جریان از طریق مقاومت سنجش جریان باید در بدن جریان یابد. این مکانیزمی است که این تنظیم را به یک تقویت کننده انتقال رسانایی تبدیل می کند (همچنین منبع جریان کنترل شده با ولتاژ ، VCCS نامیده می شود).

op-amp تنها در صورتی می تواند جریان را حفظ کند که امپدانس بدنه خیلی زیاد نباشد. در غیر این صورت خروجی op-amp فقط در ولتاژ تغذیه (0 یا 5 ولت) حداکثر می شود. حداکثر محدوده ولتاژ قابل حفظ VDD/2 + Upeak (2.5 + 1.5V = 4V @ 5V منبع تغذیه) است. حاشیه ولتاژ op-amp باید از این مقدار کم شود ، اما اگر op-amp دارای مشخصات راه آهن به راه آهن باشد ، مقدار کمی خواهد بود. بنابراین حداکثر امپدانسی که op-amp می تواند هدایت کند عبارت است از:

Z <(VDD / 2 + Upeak) / Imax

(در تنظیمات من Z <4V / 14 microAmps = 285 کیلو اهم ، آرزو برای پوشش دادن محدوده امپدانس بدن بسیار زیاد است)

مقاومت محافظ دارای ارزش بسیار زیادی (1-1.5 مگا اهم) در مقایسه با بدنه (تقریبا 100 کیلو اهم) است و برای همه عملیات عادی این جریان قابل توجهی را جذب نمی کند و امپدانس اتصال موازی تحت سلطه امپدانس بدنه است. اگر امپدانس بدنه افزایش یابد (به عنوان مثال لنت ها شل می شوند) ، جریان می تواند از طریق مقاومت عبور کند و حداکثر خروجی از am-amp ولتاژ ناخوشایندی در پدها ایجاد نمی کند.

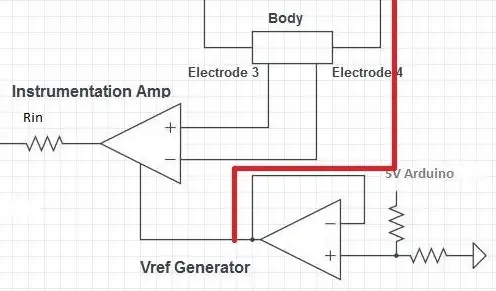

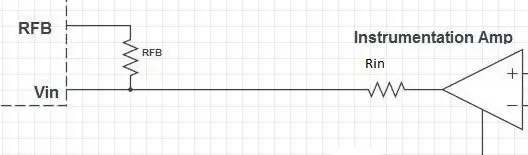

مرحله 4: تقویت کننده ابزار دقیق

مرحله بعدی تقویت کننده ابزار (درون آمپر) است که ولتاژ بدن را اندازه گیری می کند. ولتاژ روی بدن در حدود 0 ولت در حال نوسان است ، اما AD5933 نیاز به ولتاژ ورودی دارد تا در محدوده مثبت باشد. بنابراین ، آمپر یک اف سی DC VDD/2 را به سیگنال ولتاژ اندازه گیری شده اضافه می کند.

مرجع VDD/2 توسط تقسیم ولتاژ تولید می شود. هر مقاومت مقداری را می توان به شرط یکسان بودن استفاده کرد. تقسیم کننده ولتاژ توسط یک دنبال کننده ولتاژ از امپدانس بقیه مدار جدا می شود. سپس خروجی دنبال کننده ولتاژ را می توان به تقویت کننده درون آمپر و رسانایی انتقال داد.

مرحله 5: مرحله ورودی و کالیبراسیون

مرحله ورودی AD5933 حاوی یک op-amp در پیکربندی بازخورد منفی است. دو مقاومت وجود دارد: یکی سری (Rin) و دیگری موازی (RFB). افزایش op-amp توسط داده می شود

A = - RFB / Rin

مزایای op-amp ورودی و in-amp (و PGA) باید اطمینان حاصل شود که سیگنال ورودی به ADC AD5933 همیشه در 0V و VDD است.

(من از مقدار افزایش در آمپر و مقاومت استفاده می کنم که تقریباً A = 0.5 را نشان می دهد)

در AD5933 ADC سیگنال ولتاژ را به سیگنال دیجیتال تبدیل می کند. محدوده ولتاژ از 0V تا VDD به محدوده دیجیتال 0-128 (2^7) تبدیل می شود. (اسناد و مدارک در این مورد روشن نیست ، اما بررسی دقیق طرحها در [1] و برخی آزمایشها از طرف من این را تأیید می کند.)

در داخل ماژول DFT مقیاس دیگری از 256 وجود دارد (1024/4 ، نگاه کنید به [1]) قبل از اینکه نتیجه در ثبت واقعی و خیالی ذخیره شود.

با پیگیری سیگنال ولتاژ از طریق AFE ، به ADC و با استفاده از عوامل مقیاس ذکر شده در قبل ، می توان ضریب افزایش را برآورد کرد:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

ممکن است هنوز کالیبراسیون لازم باشد بنابراین برخی از اثرات این مدل ریاضی را در نظر بگیرید ، بنابراین لطفاً با اندازه گیری اجزای امپدانس شناخته شده ، مانند مقاومت ، مقدار واقعی سود را اندازه گیری کنید. (g = Z / mag ، زیر را ببینید)

امپدانس اکنون می تواند توسط محاسبه شود

Z = g * mag

mag = sqrt (واقعی^2 + خیالی^2)

PA = arctan2 (واقعی ، خیالی) - deltaPA

PA احتمالاً باید کالیبره شود و همچنین یک تغییر فاز سیستماتیک به عنوان تابعی از فرکانس در AD5933 وجود دارد. deltaPA احتمالاً تابع فرکانسی خطی خواهد بود.

اکنون می توان مقاومت و راکتانس را با استفاده از آن محاسبه کرد

R = Z * cos (PA)

X = Z * sin (PA)

منابع: [1] لئونید ماتسیف ، "بهبود عملکرد و تنوع سیستم ها بر اساس آشکارسازهای تک فرکانسی DFT مانند AD5933" ، Electronics 2015 ، 4 ، 1-34 ؛ doi: 10.3390/electronics4010001

مرحله 6: موارد پیشرفته: نشت طیفی (DC)

سیگنالی که ما در AD5933 قرار می دهیم یک ولتاژ/جریان به عنوان عملکرد زمان است ، اما علاقه اصلی ما امپدانس به عنوان یک فرکانس است. برای تبدیل بین حوزه زمانی و دامنه فرکانس ، ما نیاز به تبدیل فوریه سیگنال حوزه زمانی داریم. AD5933 دارای یک ماژول تبدیل فوریه مجزا (DFT) است. در فرکانسهای پایین (زیر حدود 10 کیلوهرتز) ساخت DFT تحت تأثیر نشت های طیفی و aliasing قرار می گیرد. در [1] او از طریق ریاضی نحوه تصحیح نشت طیفی می رود. اصل این امر محاسبه پنج (به علاوه دو) ثابت برای هر مرحله فرکانس در رفت و برگشت است. این را می توان به راحتی انجام داد ، به عنوان مثال توسط Arduino در نرم افزار

نشت به دو صورت صورت می گیرد: نشت DC که از نظر ماهیت افزودنی است و نشت AC که از نظر ماهیت چند برابر است.

نشت DC ناشی از این واقعیت است که سیگنال ولتاژ در ADC در حدود 0V نیست بلکه در اطراف VDD/2 در حال نوسان است. سطح DC VDD/2 باید مطابق با قرائت دیجیتال DC تقریبا 64 (دلتا تعیین شده در [1]) باشد.

مراحل تصحیح نشت طیفی DC:

1) ضریب پاکت E را برای فرکانس فعلی محاسبه کنید.

2) محاسبه دو عامل افزایش GI (واقعی) و GQ (خیالی)

3) دلتا * GI را از مقدار ثبت واقعی و دلتا * GQ را از مقدار ثبت خیالی کم کنید

منابع:

[1] لئونید ماتسیف ، "بهبود عملکرد و تنوع سیستم ها بر اساس

آشکارسازهای تک فرکانسی DFT مانند AD5933 ، Electronics 2015 ، 4 ، 1-34 ؛ doi: 10.3390/electronics4010001

[2] Konrad Chabowski ، Tomasz Piasecki ، Andrzej Dzierka ، Karol Nitsch ، "ساده امپدانس محدوده فرکانس گسترده بر اساس AD5933 مدار مجتمع" ، مترول. وسایل Syst. ، Vol. XXII (2015) ، شماره 1 ، صص 13-24.

مرحله 7: موارد پیشرفته: نشت طیفی (AC)

مانند نشتی DC ، نشتی AC را می توان از نظر ریاضی اصلاح کرد. در [1] مقاومت و راکتانس به ترتیب A*cos (phi) و A*sin (phi) نامیده می شود ، جایی که A مربوط به مقدار امپدانس و phi مربوط به زاویه فاز (PA) است.

مراحل تصحیح نشت طیفی AC:

1) ضریب پاکت E (نه همان DC) را برای فرکانس فعلی محاسبه کنید.

2) سه عامل a ، b و d را محاسبه کنید. (مقادیر تقریبی در فرکانسهای بالاتر: a = d = 256 و b = 0)

3) مقاومت (Acos (phi)) و راکتانس (Asin (phi)) را می توان در واحدهای دیجیتال محاسبه کرد

منابع: [1] لئونید ماتسیف ، "بهبود عملکرد و تنوع سیستم ها بر اساس آشکارسازهای تک فرکانسی DFT مانند AD5933" ، Electronics 2015 ، 4 ، 1-34 ؛ doi: 10.3390/electronics4010001

[2] Konrad Chabowski ، Tomasz Piasecki ، Andrzej Dzierka ، Karol Nitsch ، "Simple Wide Frequency Range Impedance Meter based on AD5933 Integrated Circuit" ، مترول. وسایل Syst. ، Vol. XXII (2015) ، شماره 1 ، صص 13-24.

مرحله 8: موارد پیشرفته: فاکتور سود نظری

با توجه به مدل سازی ریاضی DFT ، همچنین می توان کل AFE را به صورت ریاضی مدل کرد. از نظر ریاضی ، سیگنال ولتاژ را می توان با یک تابع سینوسی با فرکانس ثابت معین ، یک افست DC و یک نوسان AC با دامنه اوج توصیف کرد. فرکانس در طول یک مرحله فرکانس تغییر نمی کند. از آنجا که ضریب افزایش فقط اندازه امپدانس را تغییر می دهد و نه PA ، ما در اینجا به هیچ گونه تغییر فاز ناشی از سیگنال توجه نخواهیم کرد.

در اینجا خلاصه ای از سیگنال ولتاژ هنگام انتشار در AFE آورده شده است:

1) پس از مرحله بایاس مجدد ، دامنه AC هنوز Upeak = 1.5V (1V @ VDD = 3.3V) است و افکت DC به VDD/2 تغییر کرده است.

2) در مقاومت سنجش جریان ولتاژ مشابه مرحله قبلی است…

3) … اما با توجه به ولتاژ برش op-amp نوسانات AC دارای اندازه Z*Upeak/Rcurrent هستند. (ولتاژ DC با ولتاژ مرجع op -amps VDD/2 - نقطه محوری اره برقی - لغو می شود و در این قسمت از مدار به زمین مناسب تبدیل می شود)

4) Unity in-amp افست DC را به VDD/2 اضافه کرده و سیگنال را به مرحله ورودی AD5933 ارسال می کند

5) op-amp در مرحله ورودی دارای A = -RFB/Rin است و دامنه AC بنابراین می شود (Z*Upeak/Rcurrent)*(RFB/Rin)

6) درست قبل از ADC یک تقویت کننده افزایش قابل برنامه ریزی (PGA) با دو تنظیم افزایش 1 یا 5 وجود دارد. بنابراین سیگنال ولتاژ در ADC می شود: PGA*(Z*Upeak/Rcurrent)*(RFB/Rin)

ADC سیگنال v (t) را با دقت 12 بیتی به سیگنال دیجیتال x (t) = u (t) / VDD * 2^7 تبدیل می کند.

قدر A با ضریب افزایش ، k ، به صورت امپدانس Z ، به صورت A = k * Z وصل می شود و مقدار تقریبی آن k = PGA * Upeak * RFB * 2^7 / (VDD * Rcurrent * Rin) است.

اگر دوست دارید به جای g = 1 / k و Z = g * A کار کنید.

مرحله 9: موارد پیشرفته: PA Shift

در [2] آنها یک تغییر سیستماتیک در PA به عنوان تابعی از فرکانس پیدا می کنند. این به دلیل تأخیر زمانی بین DAC است که سیگنال تحریک تولید می شود و DFT که در آن سیگنال ورودی باید با سیگنال خروجی پیچیده شود.

این تغییر با تعداد چرخه های ساعت مشخص می شود که سیگنال بین DAC و DFT به صورت داخلی در AD5933 تأخیر دارد.

منابع: [1] لئونید ماتسیف ، "بهبود عملکرد و تنوع سیستم ها بر اساس آشکارسازهای تک فرکانسی DFT مانند AD5933" ، Electronics 2015 ، 4 ، 1-34 ؛ doi: 10.3390/electronics4010001

[2] Konrad Chabowski ، Tomasz Piasecki ، Andrzej Dzierka ، Karol Nitsch ، "ساده امپدانس محدوده فرکانس گسترده بر اساس AD5933 مدار مجتمع" ، مترول. وسایل Syst. ، Vol. XXII (2015) ، شماره 1 ، صص 13-24.

توصیه شده:

تجزیه و تحلیل LTE Cat.M1 PSM (حالت ذخیره انرژی): 4 مرحله

تجزیه و تحلیل LTE Cat.M1 PSM (حالت ذخیره انرژی): در مقاله قبلی ، ما نحوه تنظیم چرخه فعال / خواب با استفاده از PSM را مورد بحث قرار دادیم. لطفاً برای توضیحات سخت افزار و تنظیم PSM و فرمان AT به مقاله قبلی مراجعه کنید. (پیوند: https://www.instructables.com/id/What-Is-a-PSMPow…Ac

تجزیه و تحلیل داده های دما/رطوبت با استفاده از Ubidots و Google-Sheets: 6 مرحله

تجزیه و تحلیل داده های دما/رطوبت با استفاده از Ubidots و Google-Sheets: در این آموزش ، داده های مختلف دما و رطوبت را با استفاده از سنسور دما و رطوبت اندازه گیری می کنیم. همچنین نحوه ارسال این داده ها به Ubidots را خواهید آموخت. به طوری که می توانید آن را از هر کجا برای برنامه های مختلف تجزیه و تحلیل کنید. همچنین توسط sendin

سنسور التراسونیک تجزیه و تحلیل برای اندازه گیری فاصله: 3 مرحله

سنسور اولتراسونیک ANALOG برای اندازه گیری فاصله: این دستورالعمل ها به نحوه استفاده از سنسور اولتراسونیک متصل به آردوینو و اندازه گیری دقیق فاصله 20 تا 720 سانتی متر می پردازد

1024 نمونه تجزیه و تحلیل طیف FFT با استفاده از مراحل Atmega1284: 9

1024 نمونه FFT Spectrum Analyzer با استفاده از Atmega1284: این آموزش نسبتاً آسان (با توجه به پیچیدگی این موضوع) به شما نشان می دهد که چگونه می توانید با استفاده از یک برد نوع آردوینو (1284 باریک) و پلاتر سریال یک تجزیه کننده طیف نمونه بسیار ساده 1024 بسازید. هر نوع کمپانی آردوینو

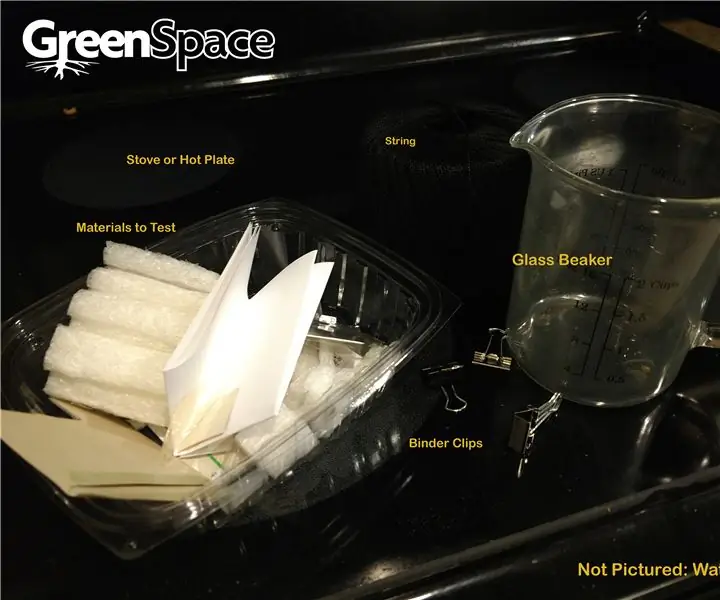

یک آزمایش تجزیه پذیری زیستی که می توانید با کودکان انجام دهید!: 8 مرحله

یک آزمایش تجزیه پذیری زیستی که می توانید با کودکان انجام دهید!: بدیهی است که آب جوش دقیقاً شبیه شرایط کمپوست یا روند کند و طبیعی تجزیه بیولوژیکی نیست. با این حال ، شما می توانید (تا حدی) نحوه تجزیه برخی مواد را در مقایسه با مواد دیگر هنگام استفاده از انرژی مانند گرما شبیه سازی کنید