فهرست مطالب:

- مرحله 1: مروری بر SPI

- مرحله 2: مشخصات طراحی

- مرحله 3: شروع به کار

- مرحله 4: نمای RTL از SPI Master Core و شبیه سازی موج

تصویری: طراحی SPI Master در VHDL: 6 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:55

در این قسمت آموزشی ، ما قصد داریم یک SPI Bus Master را از ابتدا در VHDL طراحی کنیم.

مرحله 1: مروری بر SPI

- SPI یک گذرگاه سریال همزمان است

- محبوبیت و سادگی آن را به یک استاندارد عملا در ارتباط سریال تبدیل کرد

- اتوبوس فول دوبلکس

- پروتکل ساده و در میان سریعترین گذرگاه سریال

مرحله 2: مشخصات طراحی

اینها مشخصات SPI Master است که ما قصد داریم طراحی کنیم:

- پشتیبانی از هر چهار حالت عملکرد ؛ به صورت پویا قابل تنظیم است

- فعال کردن ساعت برای صرفه جویی در مصرف برق

- طول و سرعت کلمه قابل تنظیم استاتیک

- وقفه تکی برای انتقال و دریافت

مرحله 3: شروع به کار

اول از همه ، IP ما باید دارای دو رابط باشد. یکی رابط سریال و دیگری رابط موازی است. رابط سریال متشکل از سیگنال های استاندارد de-facto استاندارد SPI است: MOSI ، MISO ، SS ، SCLK.

MOSI گاهی SDO و MISO گاهی SDI نامیده می شود.

رابط سریال برای ارتباط با لوازم جانبی خارجی ، یعنی برده های SPI استفاده می شود.

رابط موازی برای ارتباط با میزبان ما ، یعنی یک میکروکنترلر یا ریزپردازنده استفاده می شود که در واقع به استاد می گوید که چه داده هایی باید به صورت سری از طریق خطوط سریال منتقل و دریافت شوند. یعنی همه گذرگاه های داده متعلق به رابط موازی هستند.

ما یک ساعت جهانی داریم که منطق SPI داخلی را هدایت می کند ، و همچنین SCLK ، که ما آن را به صورت داخلی تولید می کنیم.

ما همچنین برخی از سیگنال های کنترل مانند نوشتن فعال ، فعال کردن ساعت را داریم. وقفه و سایر سیگنال های وضعیت.

از آنجا که ما باید با شرایط کنترل پیچیده برخورد کنیم ، طراحی IP های ارتباطی سریالی به عنوان FSM ساده تر است. ما SPI master را به عنوان FSM نیز طراحی خواهیم کرد. FSM توسط یک ساعت داخلی دیگر هدایت می شود که دو برابر SCLK است. این ساعت داخلی با استفاده از شمارنده های همزمان از ساعت جهانی تولید می شود.

همه سیگنال های کنترلی که دامنه های ساعت را متقاطع می کنند دارای هماهنگ کننده هایی هستند که در طرف امن تر قرار دارند.

مرحله 4: نمای RTL از SPI Master Core و شبیه سازی موج

این یک طراحی RTL برهنه است و از IP های FPGA اختصاصی استفاده نشده است. بنابراین یک کد کاملاً قابل حمل برای هر FPGA است.

توصیه شده:

طراحی یک کنترل کننده حافظه پنهان ساده چهار طرفه ساده در VHDL: 4 مرحله

طراحی یک کنترل کننده ساده راهپیمایی چهار طرفه ساده در VHDL: در دستورالعمل قبلی من ، نحوه طراحی یک کنترل کننده کش ساده نقشه برداری مستقیم را دیدیم. این بار ، ما یک قدم جلوتر حرکت می کنیم. ما در حال طراحی یک کنترل کننده حافظه پنهان مجموعه ای چهار طرفه ساده هستیم. مزیت - فایده - سود - منفعت ؟ نرخ از دست دادن کمتر ، اما به قیمت انجام

طراحی یک کنترل کننده وقفه قابل برنامه ریزی در VHDL: 4 مرحله

طراحی یک کنترل کننده وقفه قابل برنامه ریزی در VHDL: من از نوع پاسخ هایی که در این وبلاگ دریافت می کنم غرق شده ام. بچه ها از اینکه به وبلاگ من سر زدید و انگیزه ای برای به اشتراک گذاشتن دانش خود با شما داشتم ، متشکرم. این بار ، من قصد دارم طراحی یک ماژول جالب دیگر را که در همه SOC ها مشاهده می کنیم - Interrupt C

طراحی I2C Master در VHDL: 5 مرحله

طراحی I2C Master در VHDL: در این قسمت آموزشی ، طراحی یک استاد ساده I2C در VHDL مورد بحث قرار گرفته است. توجه: برای مشاهده تصویر کامل روی هر تصویر کلیک کنید

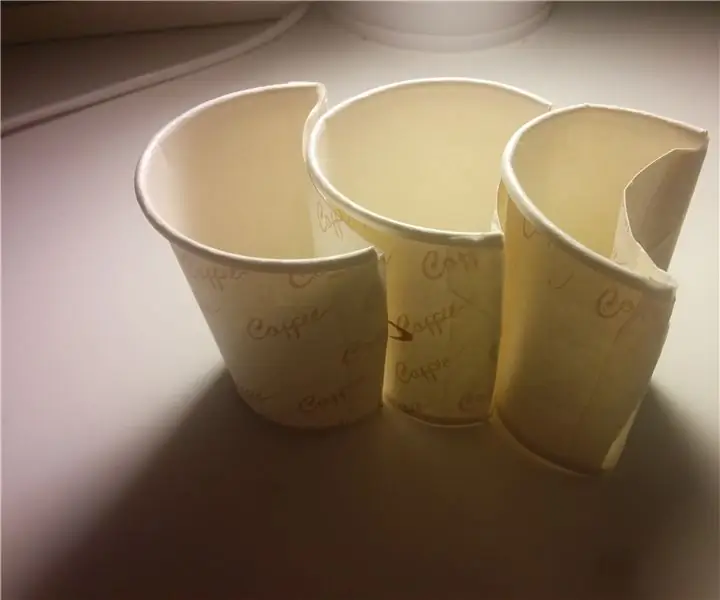

طراحی یک جام مقوایی با روش های تفکر طراحی: 7 مرحله

طراحی جام مقوایی با روش های تفکر طراحی: با سلام ، جام مقوایی که مطابق روش های تفکر طراحی طراحی شده است ، در اینجا وجود دارد. به این موضوع دقت کنید و نظر دهید لطفا. من پروژه خود را با نظرات شما بهبود می بخشم :) خیلی ممنون ---------------------------- Merhaba، Design Thinking me

قلم های طراحی نور LED: ابزارهای طراحی دودل های سبک: 6 مرحله (همراه با تصاویر)

قلم های طراحی با نور LED: ابزارهایی برای ترسیم ابله های سبک: همسرم لوری یک دودلر بی وقفه است و من سالها با عکاسی با نوردهی طولانی بازی کرده ام. با الهام از گروه هنرمندان نور PikaPika و سهولت دوربین های دیجیتال ، ما از هنر نقاشی سبک استفاده کردیم تا ببینیم چه کاری می توانیم انجام دهیم. ما یک لار