فهرست مطالب:

- مرحله 1: مرور سریع تغییرات + شماتیک

- مرحله 2: CPU ، حافظه و کنترل حافظه

- مرحله 3: LED های وضعیت سیستم

- مرحله 4: ورودی و خروجی

- مرحله 5: بازنشانی و تکمیل ورودی و خروجی

- مرحله ششم: برنامه نویسی

تصویری: بازبینی رایانه Z80: 6 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:51

در گذشته ، من راهنمای نحوه ساخت رایانه مبتنی بر Z80 را نوشتم و مدار را تا آنجا که ممکن است ساده طراحی کردم تا بتوان آن را به راحتی ساخت. من یک برنامه کوچک نیز با استفاده از همان ایده سادگی نوشتم. این طرح نسبتاً خوب کار کرد ، اما من از آن راضی نبودم. من با بازنویسی برنامه ای برای آن شروع کردم که اجازه می داد در زمان اجرا برنامه ریزی شود. این به من این امکان را می دهد که قطعات کد را بدون اختصاص آن به EEPROM آزمایش کنم ، که به نوبه خود مستلزم برنامه ریزی مجدد EEPROM است. این برای من ایده جالبی به نظر نمی رسید. سپس به فکر فضاهای حافظه افتادم. اگر بخواهم یک سخت افزار (عمدتاً IO) رابط دهی کنم ، یک قطعه کد به طور بالقوه می تواند از فضای حافظه موجود در سیستم فراتر رود. به یاد داشته باشید ، این طرح فقط از بایت پایین گذرگاه آدرس استفاده می کند و سپس بیت پایین بایت بالا برای انتخاب بین فضاهای ROM و RAM استفاده می شود. این بدان معناست که من فقط 253 بایت فضا برای استفاده داشتم. ممکن است بپرسید چرا 253 به جای 256. این به این دلیل است که کد جدید من سه بایت داده را در پایان برنامه نوشتاری تزریق می کند (این مورد بعداً بررسی می شود ، زیرا آن را تغییر دادم تا روی طرح جدید کار کنم).

n

برگشتم روی طرحواره های قدیمی ام تا ببینم دیگر چه خبر است. من یک نقص کوچک در مدار انتخاب حافظه پیدا کردم که وقتی به آنجا برسم ، آن را برطرف می کنم. نسخه ساده شده: همه درخواست های نوشتن در واقع انجام می شود ، اگرچه همیشه در RAM قرار می گیرد. این احتمالاً چیز نگران کننده ای نبود ، اما می خواستم این بار آن را به درستی انجام دهم. و با این کار ، شروع به ترسیم یک شماتیک جدید کردم. دو عکس پیوست شده به این صفحه قبل و بعد از مدار واقعی هستند. من خیلی از سیم کشی اسپاگتی را تمیز کردم ، خنده دار نیست.

n

اگر شما با ارائه اولیه من همراه بوده اید و قصد دارید با این مورد نیز همراه باشید ، از من متنفر خواهید شد. اگر تازه شروع کرده اید ، خوش شانس هستید. فقط قسمت های موجود در لیست (یا معادل آنها) را بگیرید و دنبال کنید.

تدارکات:

LM7805 - تنظیم کننده 5 ولت Z80 - CPU ؛ مغز سیستم AT28C64B - EEPROM. ذخیره اطلاعات "دائمی" مورد استفاده برای سیستم عامل کامپیوتر IDT6116SA - SRAM ؛ مورد استفاده برای ذخیره کد کاربر و /یا ذخیره سازی عمومی اطلاعات N555 - سیستم clock74HC374 - Octal D -Latch with /OE ؛ به عنوان تراشه ورودی استفاده می شود 74LS273 - Octal D -Latch with /MR؛ تراشه خروجی TLC59211 - تراشه درایور LED (استفاده می شود تا 74LS273 بتواند LED ها را هدایت کند ، زیرا به تنهایی قادر به خروجی فعلی نیست) MC14572 - این یک تراشه "Line Driver" است ، اما به نظر من برای منطق کنترل حافظه مناسب است. دارای 4 اینورتر و یک دروازه NAND و NOR ساخته شده در 74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - 12 Stage Ripple Counter؛ تقسیم کننده ساعت کشیده شده ، اما اجرا نشده است (برای اجرای سیستم با سرعت کمتر ساعت) 2 مقاومت 10 کیلو اهم - یکی در مدار تایمر 555 استفاده می شود ، بنابراین از هر مقداری که می خواهید برای آن استفاده کنید 4 مقاومت 1 کیلو اهم - یکی برای مدار تایمر 555 ، بنابراین از هر چیزی که می خواهید برای آن استفاده کنید. یکی دیگر برای رانندگی LED ها استفاده می شود ، بنابراین اگر دوست دارید 8x330 Ohm Resistor Bus8x10K Ohm Resistor Bus11 LED ها را انتخاب کنید - سه مورد برای وضعیت سیستم و هشت تای دیگر خروجی هستند. برای 8 ، من از صفحه نمایش نمودار میله ای (HDSP -4836) 4 خازن استفاده کردم - دو عدد از LM7805 استفاده می شود. 0.22uF و 0.1uF یکی مربوط به تایمر 555 است ، بنابراین از چیزی که فکر می کنید درست است استفاده کنید. آخرین مورد برای تنظیم مجدد قدرت است. 100uF2 N. O. دکمه های فشار - یکی برای ورودی و دیگری برای تنظیم مجدد 8 SPST DIP Switches - ورودی داده ها استفاده می شود. من از Piano Key styleWire استفاده کردم. تعداد زیادی سیم

n

توجه: نسخه MC14572 از طریق حفره منسوخ شده است ، اما نسخه SMD هنوز فعال است (حتی در وضعیت "نه برای طراحی جدید") ، بنابراین ممکن است لازم باشد برای استفاده از آن یک برد مدار خریداری کنید. از 74LS32 دوم می توان به جای MC14572 استفاده کرد (به "طرح انتخاب حافظه" شماتیک آی بیل قبلی مراجعه کنید)

مرحله 1: مرور سریع تغییرات + شماتیک

نحوه خواندن شماتیک: یک فلش به تراشه نشان داده شده یک ورودی است: ورودی> -یک پیکان که از تراشه دور شده است یک خروجی است: خروجی <-اتوبوس ها به جای فلش از یک خط استفاده می کنند: گذرگاه |-

n

اکثر تراشه ها با پین های دقیق خود کشیده شده اند. شیب کمی روی این تراشه ها کشیده شده است. اکثر تراشه ها دارای شماره پین و برچسب روی آن هستند. شاید خواندن آنها کمی سخت باشد. مدادم داشت کم رنگ می شد.

n

از نظر اتصالات مدار ، طرح طرح جدید عمدتا بدون تغییر در طرح اصلی است. من قسمت پایینی آدرس بایت بالا را به حافظه وصل کردم و سپس از بیت پایین نوک قسمت بالا (A12) برای انتخاب RAM/ROM استفاده کردم. این بدان معناست که فضای ROM از 0000-00FF تا 0000-0FFF افزایش یافته است. فضای رم از 0100-01FF به 1000-1FFF رسید. من همچنین منطق کنترل حافظه را برای طراحی بهتر عوض کردم و دو LED وضعیت جدید (و منطق چسب) اضافه کردم. من همچنین یک مدار تقسیم کننده ساعت کشیده ام (اما سیم نزده ام). قرار بود دو کارکرد را انجام دهد. عملکرد آشکار تقسیم فرکانس ساعت به پایین است. عملکرد دیگر برای اهداف PWM (مدولاسیون عرض پالس) است ، زیرا 555 امواج را با 50 درصد چرخه کار تولید نمی کند. این در این مدار واقعاً مهم نیست ، اما اگر بخواهید از ساعت برای رانندگی برخی از LED ها استفاده کنید ، مطمئناً متوجه اثرات می شوید (یکی (مجموعه ای از LED ها) از دیگری کم نورتر خواهد بود). بقیه مدارها اساساً بدون تغییر هستند.

مرحله 2: CPU ، حافظه و کنترل حافظه

این بخشی است که خوانندگان نسخه قبلی من از من متنفر هستند. در ساخت اولیه ، من فقط قسمتی را روی تخته در جایی انداختم که به نظر می رسید مشکل چندانی در مورد سیم کشی ندارند. نتیجه به نظر می رسید که فردی بشقاب اسپاگتی را روی آن ریخته و شبیه "سیم" است. من می خواستم آن را کمی تمیز کنم ، بنابراین با ریپ کردن همه چیز به جز CPU ، RAM و ROM شروع کردم. من تقریباً کل مدار ورودی ، مدار خروجی و منطق چسب را بیرون کشیدم. انجام آن تقریباً به من صدمه زد ، اما لازم بود. تمام اتصالات داده را دست نخورده و بایت پایین تر از گذرگاه آدرس را رها کردم. سپس چهار بیت بعدی گذرگاه آدرس (A8-A11) را به تراشه ROM متصل کردم. این بار مراقب بودم که تراشه را دور بزنم تا برنامه ریزی مجدد راحت تر شود. همچنین اتصالات آدرس را به تراشه RAM پرت کردم.

n

با این کار ، من مجبور شدم منطق کنترل حافظه را به هم متصل کنم. در شماتیک اصلی ، من خط پردازنده /MREQ را مستقیماً به /CE به هر دو تراشه حافظه وصل کرده بودم ، سپس /WR را به RAM /WE وصل کردم. سپس من CPU /RD و /MREQ منطقی OR'd و A9 را با هم داشتم. اساساً ، به گونه ای تنظیم شده بود که همه درخواست های حافظه ، RAM و ROM را فعال می کردند ، اما A9 برای انتخاب کدام یک از تراشه ها /OE انتخاب شد. این خوب بود و همه اینها به این دلیل بود که تراشه ها تا زمان درخواست حافظه غیرفعال می ماندند و سپس فقط یک /OE در طول یک درخواست خواندن فعال می شد. این مانع از گفتگوی متقابل شد ، اما یک تفاوت ظریف را ایجاد کرد. از آنجا که A9 فقط برای تعیین اینکه کدام تراشه داده ها را خارج می کند استفاده می شود و زیرا CPU مستقیماً به پین RAM /WE دسترسی داشت ، هرگونه درخواست نوشتن انجام می شود. این برای ROM مناسب بود زیرا حالت نوشتن آن با اتصال مستقیم WE به منبع تغذیه 5 ولت مهار می شود. با این حال ، RAM بدون در نظر گرفتن A9 نوشته می شود. این بدان معنی است که تلاش برای نوشتن در یک مکان فضای ROM در همان مکان در فضای RAM ارسال می شود.

n

یک راه حل برای این امر این است که منطق کنترل را دوباره وصل کنید تا پردازنده بتواند مستقیماً به پین های تراشه /OE و /WE دسترسی داشته باشد و سپس از MREQ و A12 برای انتخاب تراشه ها /CE استفاده کند. من با این ایده پیش رفتم ، اما به جای استفاده از چهار دروازه NOR و اینورتر مانند طرح اصلی ، یک تراشه کوچک ناخوشایند پیدا کردم که برای این کار مناسب بود. من مجبور شدم مداری ایجاد کنم که فقط از دروازه های منطقی موجود در تراشه استفاده می کرد ، اما این به اندازه کافی آسان بود. A12 به طور مستقیم به یک دروازه NAND و یک دروازه NOR تغذیه می شود. /MREQ در دروازه NOR و تعریف آن در دروازه NAND تغذیه می شود. دروازه NAND برای رانندگی /CE برای RAM استفاده می شود و خروجی NOR معکوس می شود و برای رانندگی ROM /CE استفاده می شود. این باعث می شود که /MREQ قبل از انتخاب هر یک از تراشه ها کم باشد و سپس A12 انتخاب می کند که کدام یک انتخاب می شود. با این راه اندازی ، اکنون هرگونه درخواست نوشتن به ROM هیچ کاری انجام نمی دهد. همچنین در مصرف برق صرفه جویی می شود زیرا فقط یک تراشه به جای هر دو فعال است. در مورد تراشه منطقی ، ما هنوز دو اینورتر بلااستفاده در داخل داریم. یکی بعداً عادت می کند ، اما وقتی به آنجا می رسیم ، به آنجا می رسیم.

مرحله 3: LED های وضعیت سیستم

قبل از شروع این پروژه ، سعی می کردم با یک IC خاص ارتباط برقرار کنم ، اما با آن مشکل داشتم. مطمئن نبودم که چه اتفاقی در حال رخ دادن است ، من از یک چراغ پنل LED برای کاوش در اطراف (یکی از مجموعه هایی که دارای مقاومت داخلی است) استفاده کردم. انجام این کار یک ایده نوستالژی به من داد که امروزه هنوز مورد استفاده قرار می گیرد: LED های وضعیتی برای نشان دادن اینکه آیا حافظه در حال خواندن است یا برای آن نوشته شده است استفاده می شد. قرار بود در ارتباط با LED ورودی که قبلاً داشتم استفاده شود. LED ورودی به ژنراتور سیگنال /WAIT متصل بود تا به ما نشان دهد که سیستم ، منتظر ورودی است (من به آنجا می رسم ، نگران نباشید). من افزودن LED برای نشان دادن نوشتن IO را در نظر گرفتم ، اما فکر کردم تغییر LED های خروجی در حال حاضر یک شاخص عالی برای آن است. با فکر کردن به آن ، ممکن است هنوز آن را اضافه کنم. با این وجود ، من مفید می دانم که بدانم حافظه در حال خواندن یا نوشتن است. خوب ، به هر حال برای اشکال زدایی برنامه مفید است. من واقعاً هنگام تلاش برای به کار انداختن برنامه خود از آن به شدت استفاده کردم: "چرا این برنامه برای حافظه می نویسد؟ قرار نیست هنوز این کار را انجام دهد!"

n

برای کنترل این LED ها ، از دروازه quad NOR استفاده کردم. من از همه دروازه ها استفاده کردم. فقط دو عدد برای تولید سیگنال های وضعیت استفاده شد ، اما تراشه از قدرت کافی برای هدایت LED ها برخوردار نیست. آنها می توانند قدرت زیادی را از بین ببرند ، بنابراین من از دو دروازه NOR دیگر به عنوان اینورتر استفاده کردم و LED ها را به همین ترتیب وصل کردم. از آنجا که یک LED برای نشان دادن خواندن و دیگری برای نوشتن استفاده می شود و درخواست خواندن و نوشتن همزمان رخ نمی دهد ، من توانستم تنها با استفاده از یک مقاومت برای هر دو LED از بین بروم. در مورد سیگنال های مورد نیاز برای رمزگشایی ، این نیز به اندازه کافی آسان بود. من می خواستم تمام درخواست های خواندن حافظه نشان داده شوند ، بنابراین اولین دروازه NOR دارای ورودی های MREQ و /RD بود. وضعیت نوشتن کمی پیچیده تر بود ، اما به همین راحتی. من هنوز از /MREQ به عنوان یک ورودی استفاده می کنم ، اما استفاده از /WR به عنوان ورودی دیگر باعث ایجاد یک تفاوت جزئی می شود که می خواستم از آن اجتناب کنم. این نشان می دهد ALL درخواست نوشتن. من فقط مواردی را می خواستم که واقعاً از بین رفته اند. پس چگونه این کار را انجام دهم؟ خوب ، به یاد دارید که چگونه سیستم را طوری تنظیم کرده ام که فقط RAM را می توان نوشت؟ من از RAM /CE به عنوان ورودی دیگر دروازه NOR استفاده کردم. این بدان معناست که LED تنها زمانی روشن می شود که RAM انتخاب شده و درخواست نوشتن در حال انجام است. از نظر رنگ LED ، نارنجی را به عنوان نشانگر خواندن (اما فقط زردها را پیدا کردم) و قرمز را به عنوان نشانگر نوشتن انتخاب کردم.

مرحله 4: ورودی و خروجی

در مرحله قبل ، ممکن است متوجه شده باشید که من بقیه اجزا را به برد اضافه کرده ام. من فضا را رزرو می کردم تا به طور تصادفی سیمها را در جایی که می خواهم یک جزء قرار دهم قرار ندهم (بنابراین باید مکان جدیدی برای جزء مذکور پیدا کنم). شاید متوجه شده باشید که من کلیدهای ورودی را در جای خود رها کرده و به سیم برق متصل کرده ام. من تصمیم گرفتم که مکان اصلی بهترین مکان است و تصمیم گرفتم LED های خروجی را در نزدیکی (بالا) قرار دهم. در سمت راست صفحه نوار ، قفل ورودی قرار دارد. بالای آن چفت خروجی و در سمت چپ آن درایور LED قرار دارد. من با اتصال صفحه نمایش به درایور شروع کردم زیرا این ساده ترین کار بود. سپس سوئیچ ها را به طرف ورودی قفل ورودی وصل کردم. بعد سمت خروجی قفل خروجی را به درایور LED وصل کردم. این ممکن است یک دستور ناخوشایند به نظر برسد ، اما این یک دلیل بود. ورودی قفل خروجی قرار بود به گذرگاه داده و همچنین خروجی قفل ورودی متصل شود. ایده این بود که خروجی های قفل ورودی را به ورودی های قفل خروجی متصل کنم ، که من این کار را کردم. سپس تنها کاری که باید انجام می دادم این بود که آن آشفتگی را به گذرگاه داده متصل کنم. مهم نیست که این اتصالات از نظر فیزیکی به کجا می روند زیرا همه آنها از نظر الکتریکی متصل می شوند. کامپیوتر در حال حاضر تقریباً تمام شده است.

مرحله 5: بازنشانی و تکمیل ورودی و خروجی

با عرض پوزش ، عکسی برای این مرحله وجود ندارد. برای عکس ها به مرحله قبل مراجعه کنید.

n

شاید در آخرین عکس مرحله قبل متوجه شده باشید که من یک دکمه سبز رنگ و یک تراشه منطقی دیگر نصب کرده بودم. تراشه دروازه OR است. دو دروازه برای تولید سیگنال /WAIT استفاده می شود. خوب ، یکی سیگنال را با OR-ing /IORQ و /RD از پردازنده تولید می کند. خروجی به دومین دروازه وارد می شود ، جایی که دوباره OR'd را به یک دکمه فشار می دهد. دکمه ورودی دروازه را بالا می آورد ، بنابراین خروجی را بالا می آورد. این خروجی به پردازنده /پین WAIT تغذیه می شود. در حالی که فشار داده نشده است ، یک مقاومت ورودی را پایین نگه می دارد. من در ابتدا از یک مقاومت 10K استفاده کردم ، اما LS32 در واقع ولتاژ را روی ورودی ایجاد می کرد. مقاومت آن را به اندازه کافی پایین نیاورد و مجبور شدم آن را با 1K جایگزین کنم. به هر حال ، ایده این است که وقتی یک درخواست خواندن IO انجام می شود ، دروازه های اول و دوم OR به پردازنده می گوید منتظر بمانید. هنگامی که سوئیچ های ورودی را روی هر چیزی که می خواهید تنظیم می کنید ، دکمه را فشار داده و CPU را از حالت انتظار خارج می کند. چراغ سبز "ورودی" ، همانطور که قبلاً آن را نام بردم ، سیم دار است به طوری که وقتی پین /WAIT پایین می رود ، روشن می شود.

n

اما ما هنوز کارمان را تمام نکرده ایم. فلیپ فلاپ ورودی به سیگنالی احتیاج دارد که زمان ورود داده ها معتبر باشد و باید به CPU ارسال شود. این پین ساعت فعال است. قبلاً فقط آن را به دکمه وصل کردیم. این هنوز یک گزینه معتبر است ، اما این بار من تصمیم گرفتم آن را در خروجی مشابه دروازه دوم OR قرار دهم. این IC همچنین دارای پین /OE است که باید رانده شود. اگر قرار بود بالا نگه داشته شود ، هرگز داده ای را به گذرگاه وارد نمی کند. اگر پایین نگه داشته شود ، همیشه با اتوبوس رانندگی می کند. برای رفع این مشکل ، من به سادگی از سومین دروازه OR استفاده کردم. ورودی ها /IORQ و /RD هستند و خروجی مستقیماً به لچ /OE می رود.

n

قفل خروجی نیز برای حرکت نیاز به پین ساعت دارد. مجدداً فعال است. در شماتیک من ، چهارمین دروازه OR را مستقیماً با استفاده از /IORQ و /WR پین را ترسیم کردم. این بدان معناست که پین ساعت تا زمانی که درخواست نوشتن داده نشود ، بالا نگه داشته می شود ، سپس دوباره پایین و سپس بالا می رود. این احتمالاً خوب خواهد بود زیرا گذر داده هنوز بلافاصله پس از تلاش برای نوشتن داده های معتبر روی آن وجود داشت ، اما از نظر مهندسی ، یک طرح زباله بود. من بعد از گرفتن عکس های نهایی متوجه این خطا نشدم ، اما آن اتصال را پاره کردم و سپس خروجی دروازه OR را از منطق کنترل حافظه به یکی از اینورترهای بلااستفاده وارد کردم ، سپس خروجی آن را به پین ساعت وصل کردم. به همچنین شماتیک را اصلاح کردم و خطای دیگری را که مرتکب شده بودم پیدا کردم. من هم تصحیحش کردم

n

با انجام همه این کارها ، من کار بسیار کمی برای انجام دادن داشتم: مدار تنظیم مجدد. من یک دکمه به برد اضافه کردم و از یک مقاومت 10K برای نگه داشتن یک طرف بالا استفاده کردم. طرف دیگر مستقیماً به زمین می رود. طرف بالا خروجی /RESET است که به هر تراشه با پین /RESET (CPU و قفل خروجی) می رسد. برای انجام تنظیم مجدد ، خازنی را به خروجی /RESET اضافه کردم. ایده این است که مقاومت مقدار زیاد باعث می شود خازن نسبتاً بزرگ به آرامی شارژ شود و پین های /RESET را برای برخی از چرخه های ساعت پایین نگه دارد (CPU به چهار چرخه ساعت نیاز دارد). احتمالاً می توانید حدس بزنید که جنبه منفی این مدار چیست. این همان منفی نسخه قبلی است زیرا همان مدار است. وقتی دکمه فشرده می شود ، خازن اساساً از طریق دکمه کوتاه می شود. این برای کلاه و دکمه بد است ، بنابراین اگر می خواهید ساختمان خود را کمی ماندگارتر کنید ، ممکن است بخواهید آن را دوباره طراحی کنید. من به تایمر 555 دیگری فکر می کردم که در حالت یکنواخت تنظیم شده بود. اما با این کار ، مدار کامپیوتر در حال حاضر به پایان رسیده است. بله در حال حاضر نیاز به برنامه دارد.

مرحله ششم: برنامه نویسی

برنامه نویسی این چیز یک کابوس بود. من یک برنامه نویس Arduino EEPROM ساختم. کار نکرد من یکی دیگر را بر اساس طراحی و کدنویسی شخص دیگری ساختم. هنوز کار نکرد من به روش آزمایش شده تنظیم دستی دستی آدرسها و بایتهای داده با دست برگشتم. به نوعی ، من آن را به هم ریختم. دوباره امتحان کردم و باز هم اشتباه کردم. من دوباره برگشتم و متوجه شدم که یک بایت خاموش است ، بنابراین آن را اصلاح کردم و در نهایت کار کرد ، خدا را شکر.

n

در مورد برنامه واقعی ، به نظر می رسد که بسیار پیچیده است و دنبال کردن آن دشوار است ، اما اینطور نیست. در واقع بسیار ساده است نیمی از آن کپی اعداد اطراف است. نیمی دیگر بین ریاضیات 16 بیتی ، جهش های مشروط و حتی کپی بیشتر اعداد در اطراف تقسیم می شود. بنابراین اجازه دهید آن را مرور کنم و نحوه عملکرد آن را به شما بگویم.

n

مقدار دهی اولیه فقط مقداری ثبات برای استفاده توسط برنامه تعیین می کند. حلقه برنامه کمی پیچیده تر است ، اما نه چندان زیاد. ابتدا ، ورودی ثبت A در پورت 00 را می پذیرد. سپس ثبت E در حافظه نوشته می شود. در دو حلقه اول ، ثبت E شامل داده های ناخواسته است ، بنابراین ما سعی می کنیم آن را در دو بایت آخر فضای ROM بنویسیم زیرا در واقع نوشته نمی شود. سپس نشانگر آدرس (IY) افزایش می یابد. سپس مقدار ذخیره شده در D به E منتقل می شود تا بعدی نوشته شود. سپس A در D بارگذاری می شود و L و E در H. HL کپی می شود ، جایی که مقایسه مقدار از طریق تفریق و بررسی ZF (پرچم صفر) صورت می گیرد. اولین مقداری که در مقایسه با آن ذخیره می شود ، در ثبت B و C. ذخیره می شود. اگر مقادیر یکسان باشند ، برنامه مستقیماً وارد فضای RAM می شود ، جایی که فرض می شود کد کاربر در آن قرار دارد. اگر کد در BC مطابقت ندارد ، HL با مقادیر اولیه از D و E بارگیری می شود و مجدداً با مقدار SP مقایسه می شود. اگر مطابقت داشته باشد ، نتیجه یکسانی دارد ، اما سه بایت اضافی در حافظه نوشته می شود. بایت ها کدی هستند که باعث می شود CPU به همان ابتدای برنامه خود بازگردد (تنظیم مجدد نرم افزار). اگر مقایسه دوم مطابقت نداشته باشد ، برنامه به جایی می رسد که از کاربر مقدار دریافت می کند.

n

LD SP ، EDBFH ؛ کد exe (اضافه کردن پرش)

n

LD IY ، FFEH ؛ اشاره گر حافظه اولیه برای ذخیره کد

n

LD BC ، EDC3H ؛ کد exe (بدون حلقه)

n

حلقه ؛ دستورالعمل اسمبلر ، بنابراین لازم نیست بدانیم که این قسمت در کجا در حافظه قرار دارد

n

در A ، (00H) ؛ دریافت اطلاعات برنامه

n

LD (IY+00H) ، E ؛ E شامل کدی است که باید ذخیره شود

n

INC IY ؛ حرکت به مکان حافظه بعدی

n

LD E ، D ؛ l را به E وارد کنید

n

LD D ، A ؛ ld A به D

n

LD H ، E ؛ ld E به H

n

LD L ، D ؛ ld D به L

n

یا A ؛ بازنشانی پرچم حمل

n

SBC HL ، BC ؛ اگر کد exe 2 وارد شده باشد 0 را برمی گرداند

n

JP Z ، 1000H ؛ اگر چنین است ، به برنامه بروید و اجرا کنید

n

LD H ، E ؛ در غیر این صورت ، اینها را به مقادیر مناسب بازخوانی کنید

n

LD L ، D

n

یا A ؛ تفریق اول ممکن است پرچم حمل را تنظیم کرده باشد. پاکش کن

n

SBC HL ، SP ؛ اگر کد exe 1 وارد شده باشد 0 را برمی گرداند

n

JP NZ ، حلقه ؛ در غیر این صورت ، فرآیند را تکرار کنید (با بدست آوردن مقدار شروع کنید)

n

LD (IY+00H) ، C3H ؛ در غیر این صورت ، یک کد پرش در پایان برنامه کاربر تزریق کنید

n

LD (IY+01H) ، 00H ؛ jump اساساً به عنوان تنظیم مجدد نرم افزار عمل می کند

n

LD (IY+02H) ، 00H ؛ در صورت تغییر رجیسترها ، این یک تنظیم مجدد کامل است

n

JP 1000H ؛ پرش به برنامه کاربر و اجرای آن

توصیه شده:

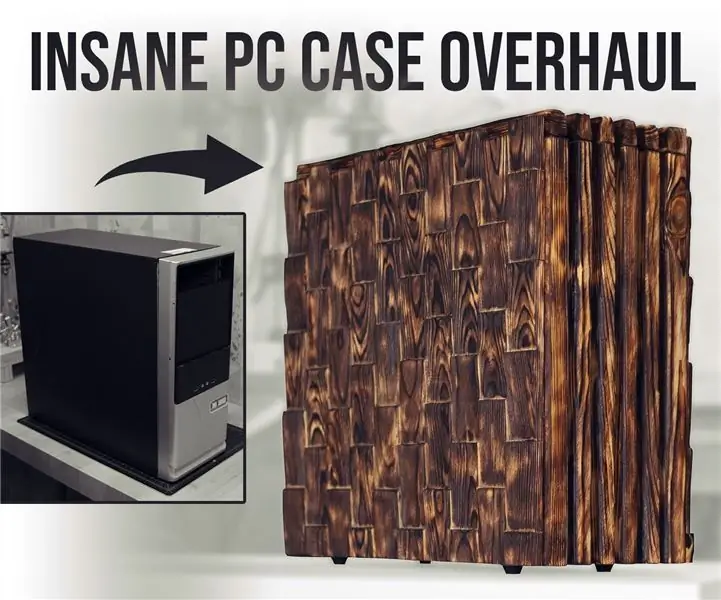

بازبینی موردی Insane PC: 23 مرحله (همراه با تصاویر)

تعمیرات اساسی در مورد رایانه شخصی: در این فیلم آموزشی/آموزشی ، من یک تغییر نسبتاً ساده برای ایجاد ظاهری متفاوت برای رایانه رومیزی قدیمی انجام خواهم داد. اما این فقط برای ظاهر نیست. جریان هوا برای اجزای داخلی نیز کیلومترها بهتر خواهد بود. و این اجازه می دهد p

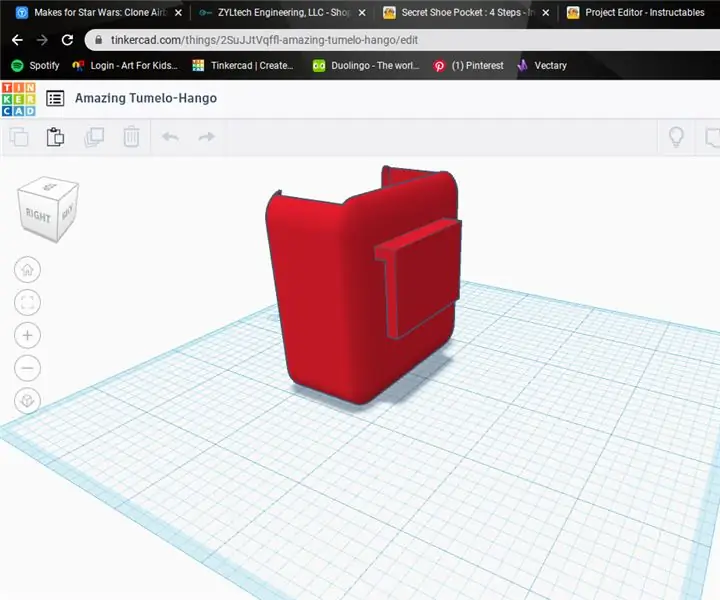

گوش نگهدارنده گوش (رایانه لوحی ، رایانه ، تلفن): 4 مرحله

نگهدارنده گوش (رایانه لوحی ، رایانه ، تلفن): من همیشه وقتی گوشواره هایم به هم می خورد یا گم می شود ، ناامید می شوم. بنابراین تصمیم گرفتم چیزی تهیه کنم که بتوانید پشت تبلت کامپیوتر خود قرار دهید و غیره

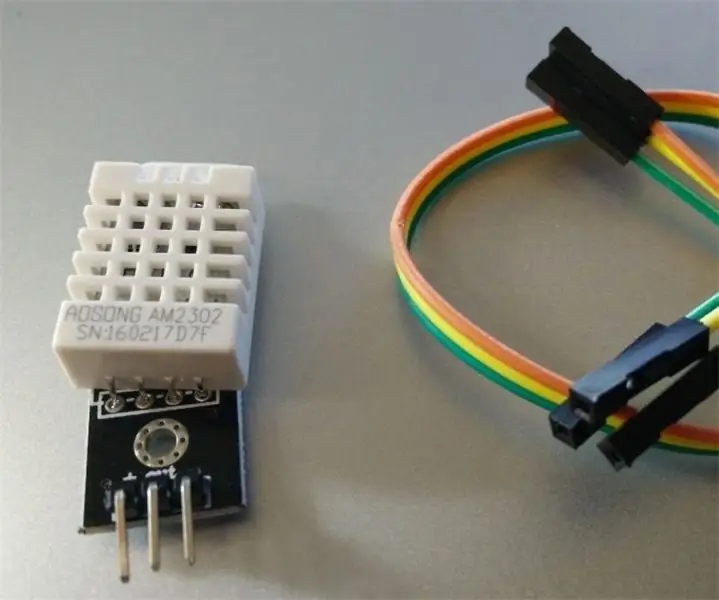

فراتر رفتن از استاندارد Firmata - بازبینی شده: 5 مرحله

فراتر از استانداردFirmata - بازبینی شده: چندی پیش ، دکتر Martyn Wheeler ، کاربر pymata4 ، با من تماس گرفت تا راهنمایی در مورد افزودن پشتیبانی از حسگر DHT22 رطوبت/دما به کتابخانه pymata4 دریافت کند. کتابخانه pymata4 ، همراه با همتای Arduino خود ، FirmataExpre

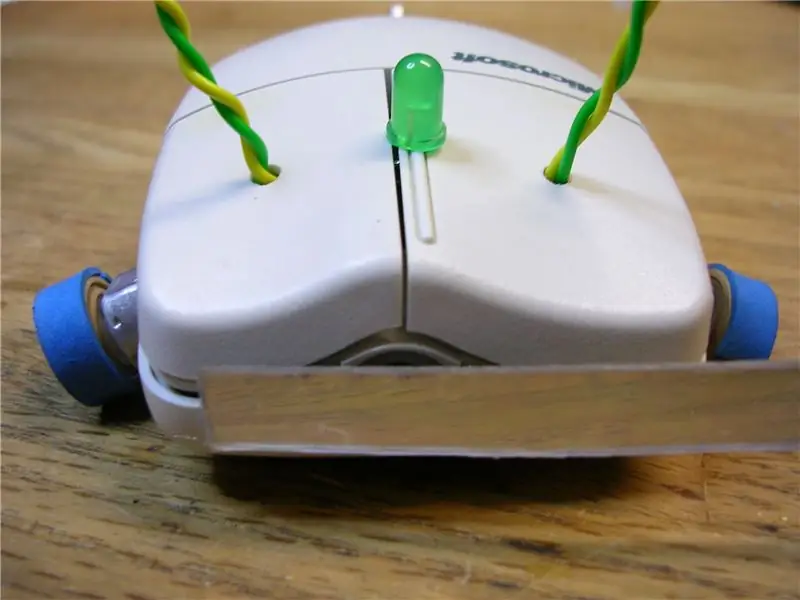

بازبینی Mousebot: 10 مرحله (همراه با تصاویر)

Mousebot Revisited: Mousebot from Make vol 2 مقدمه ای سرگرم کننده برای رباتیک است. آنقدر سرگرم کننده است که من این مستندات گسترده از ساخت Mousey را از ابتدا تا انتها ایجاد کرده ام ، با چند نکته اضافی اضافی که در mag پیدا نمی کنید. این نحوه انجام را بهتر می توان پس از واقعیات درک کرد

از SSH و XMing برای نمایش برنامه های X از رایانه لینوکس در رایانه Windows استفاده کنید: 6 مرحله

از SSH و XMing برای نمایش برنامه های X از رایانه لینوکس در رایانه Windows استفاده کنید: & nbsp؛ اگر در محل کار از لینوکس و در خانه از ویندوز استفاده می کنید یا برعکس ، ممکن است در مواقعی دیگر نیاز به ورود به رایانه داشته باشید. ، و برنامه ها را اجرا کنید. خوب ، می توانید X Server را نصب کرده و SSH Tunneling را با SSH Client خود فعال کنید ، و یکی