فهرست مطالب:

- مرحله 1: معماری ADC

- مرحله 2: مدار داخلی

- مرحله 3: مدار خارجی

- مرحله 4: دستورالعمل های I2C را بخوانید

- مرحله 5: نتایج

تصویری: نحوه ایجاد ADC در حال حاضر: 5 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:53

در این دستورالعمل نحوه پیاده سازی مبدل 8 بیتی آنالوگ به دیجیتال (ADC) در SLG46855V را توضیح می دهیم که می تواند جریان بار و رابط کاربری را با MCU از طریق I2C حس کند. از این طرح می توان برای کاربردهای مختلف سنجش جریان مانند آمپرمتر ، سیستم های تشخیص خطا و سنج های سوخت استفاده کرد.

در زیر مراحل مورد نیاز برای درک نحوه برنامه ریزی راه حل برای ایجاد حس فعلی ADC را شرح دادیم. با این حال ، اگر فقط می خواهید نتیجه برنامه نویسی را دریافت کنید ، نرم افزار GreenPAK را بارگیری کنید تا فایل طراحی GreenPAK را که قبلاً تکمیل شده است مشاهده کنید. کیت توسعه GreenPAK را به رایانه خود وصل کرده و برنامه را بزنید تا حس فعلی ADC ایجاد شود.

مرحله 1: معماری ADC

ADC اساساً از یک مقایسه کننده آنالوگ و یک مبدل دیجیتال به آنالوگ (DAC) تشکیل شده است. مقایسه کننده ولتاژ ورودی را در مقابل ولتاژ خروجی DAC حس می کند و متعاقباً کنترل می کند که کد ورودی DAC را افزایش یا کاهش دهد ، به طوری که خروجی DAC به ولتاژ ورودی همگرا می شود. کد ورودی DAC به کد خروجی دیجیتال ADC تبدیل می شود.

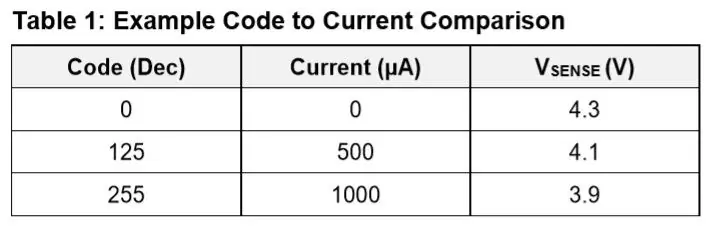

در اجرای ما ، ما یک DAC با استفاده از یک شبکه مقاومت کنترل شده با مدولاسیون عرض پالس (PWM) ایجاد می کنیم. ما به راحتی می توانیم با استفاده از GreenPAK یک خروجی PWM با کنترل دیجیتالی دقیق ایجاد کنیم. PWM وقتی فیلتر می شود ولتاژ آنالوگ ما می شود و بنابراین به عنوان یک DAC موثر عمل می کند. مزیت بارز این روش این است که به راحتی می توان ولتاژهایی را که مطابق با کد صفر و مقیاس کامل (معادل افست و افزایش) است تنظیم کرد ، به سادگی تنظیم مقادیر مقاومت. به عنوان مثال ، یک کاربر می خواهد در حالت ایده آل کد صفر را از سنسور دما بدون جریان (0 µA) مربوط به 4.3 ولت و کد در مقیاس کامل در 1000 µA مربوط به 3.9 V بخواند (جدول 1). این امر به سادگی با تنظیم چند مقدار مقاومت قابل اجرا است. با مطابقت دامنه ADC با محدوده سنسور مورد علاقه ، ما از وضوح ADC بیشترین استفاده را می کنیم.

یک ملاحظه طراحی برای این معماری این است که فرکانس PWM داخلی باید بسیار سریعتر از نرخ به روز رسانی ADC باشد تا از رفتار کم نور حلقه کنترل آن جلوگیری شود. حداقل باید بیشتر از ساعت شمارنده داده ADC تقسیم بر 256 باشد. در این طرح ، دوره به روز رسانی ADC روی 1.3312 میلی ثانیه تنظیم شده است.

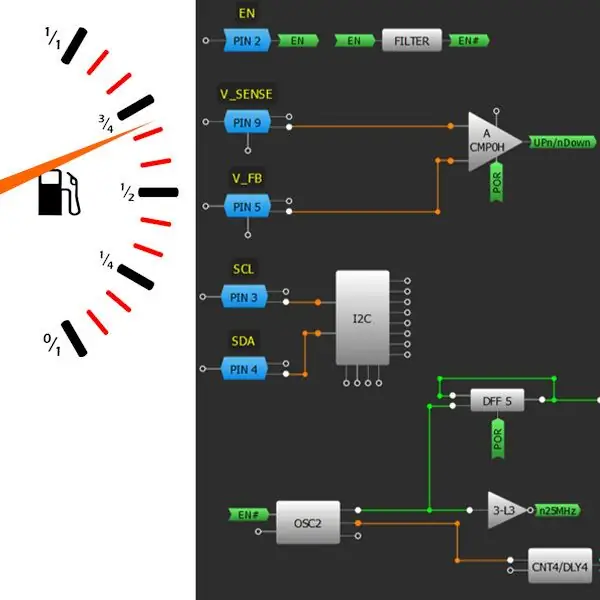

مرحله 2: مدار داخلی

ADC انعطاف پذیر بر اساس طرح ارائه شده در Dialog Semiconductor AN-1177 است. سرعت کلاک از 1 مگاهرتز به 12.5 مگاهرتز افزایش می یابد تا بتواند شمارنده ADC را تنظیم کند زیرا SLG46855 دارای یک ساعت 25 مگاهرتز در دسترس است. این اجازه می دهد تا سرعت به روز رسانی بسیار بیشتری برای وضوح نمونه بهتر داشته باشید. زمان سنج LUT ساعت داده ADC را تغییر می دهد بنابراین هنگامی که PWM DFF کم است از سیگنال 12.5 مگاهرتز عبور می کند.

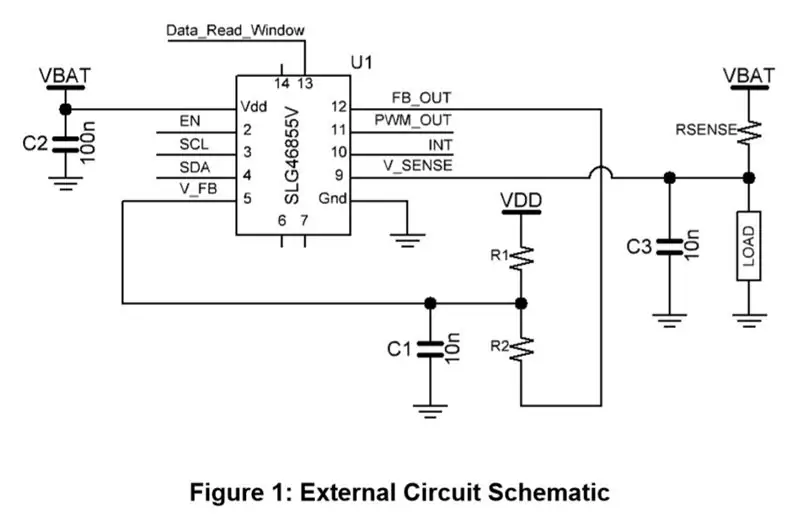

مرحله 3: مدار خارجی

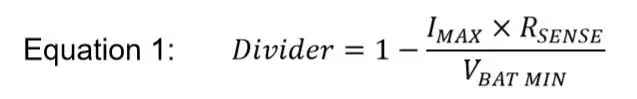

از یک مقاومت خارجی و شبکه خازنی برای تبدیل PWM به ولتاژ آنالوگ استفاده می شود که در شکل شماتیک مدار در شکل 1 نشان داده شده است. مقادیر حداکثر رزولوشن برای حداکثر جریانی که دستگاه حس می کند محاسبه می شود. برای دستیابی به این انعطاف پذیری ، مقاومت R1 و R2 را به موازات VDD و زمین اضافه می کنیم. تقسیم کننده مقاومت VBAT را به سمت پایین محدوده ولتاژ تقسیم می کند. نسبت تقسیم برای حداقل VBAT مورد انتظار را می توان با استفاده از معادله 1 حل کرد.

مرحله 4: دستورالعمل های I2C را بخوانید

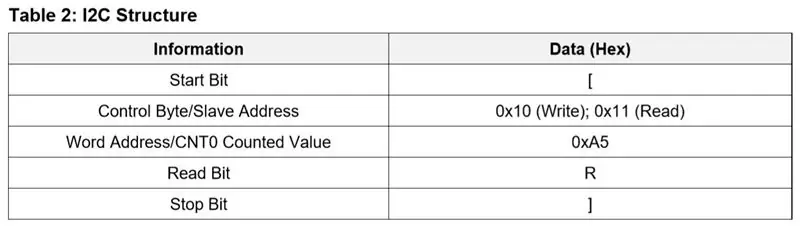

جدول 1 ساختار فرمان I2C را برای بازخوانی داده های ذخیره شده در CNT0 توضیح می دهد. دستورات I2C به بیت شروع ، بایت کنترل ، آدرس کلمه ، بیت خواندن و بیت توقف نیاز دارد.

یک مثال I2C برای بازخوانی مقدار شمارش شده CNT0 در زیر نوشته شده است:

[0x10 0xA5] [0x11 R]

مقدار شمارش شده که بازخوانی می شود مقدار کد ADC خواهد بود. به عنوان مثال ، یک کد آردوینو در فایل ZIP این یادداشت برنامه در وب سایت Dialog گنجانده شده است.

مرحله 5: نتایج

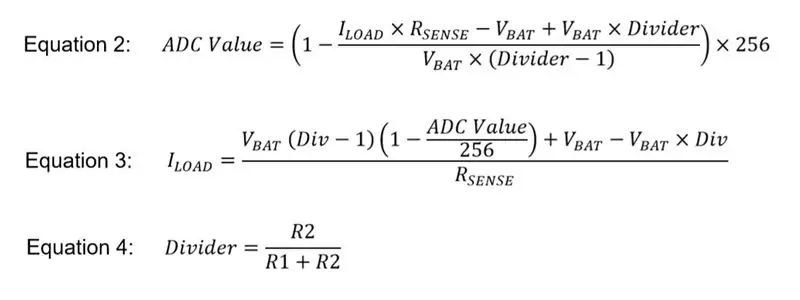

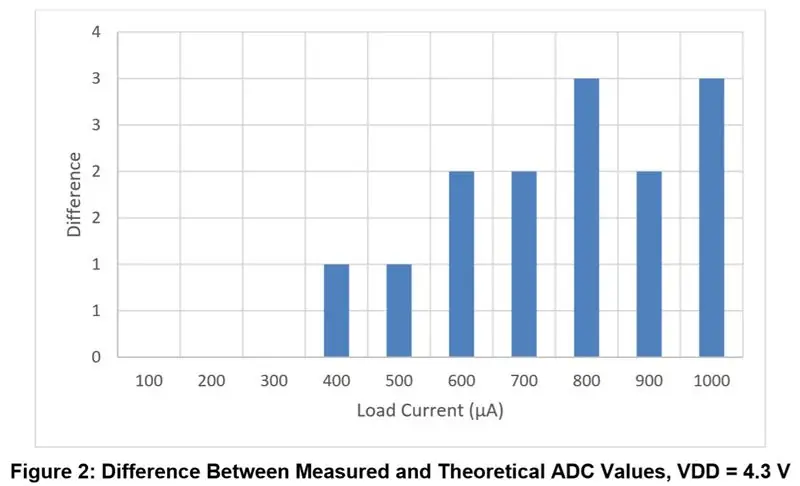

برای آزمایش دقت طراحی حس کنونی ADC ، مقادیر اندازه گیری شده در جریان بار معین و سطح VDD با مقدار نظری مقایسه شد. مقادیر ADC نظری با معادله 2 محاسبه شد.

ILOAD که با مقدار ADC ارتباط دارد با معادله 3 یافت می شود.

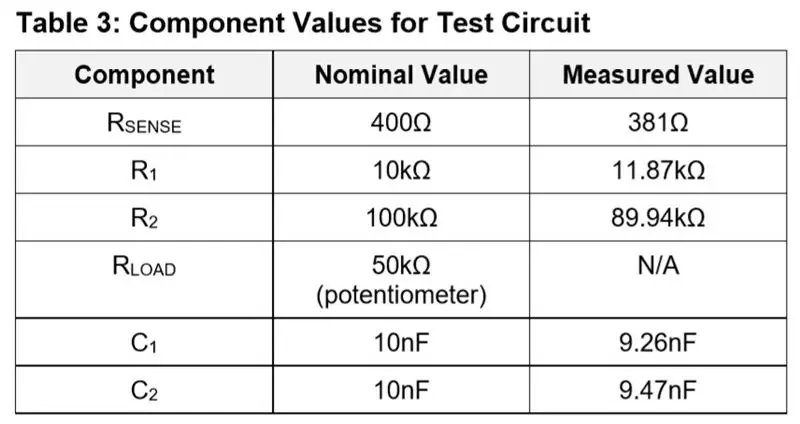

برای نتایج زیر از این مقادیر م componentلفه نشان داده شده در جدول 3 استفاده کردم.

وضوح مقدار ADC به تبدیل ILOAD را می توان با استفاده از معادله 3 با مقادیر اندازه گیری شده در جدول 2 و مقدار ADC برابر 1 محاسبه کرد. با VBAT 3.9 ولت وضوح تصویر 4.96 µA/div است.

به منظور بهینه سازی مدار حسی جریان ADC به حداقل سطح VDD 3.6 ولت با حداکثر جریان 1100 µA و مقاومت حسگر 381 Ω ، ضریب تقسیم ایده آل 0.884 ، بر اساس معادله 1. با مقادیر داده شده در جدول 2 ، تقسیم کننده واقعی دارای ضریب تقسیم 0.876 است. از آنجا که این مقدار کمی کمتر است ، محدوده جریان بار کمی بیشتر را امکان پذیر می کند ، بنابراین مقادیر ADC به محدوده کامل نزدیک است اما سرریز نمی شود. مقدار تقسیم کننده واقعی با معادله 4 محاسبه می شود.

در بالا (شکلهای 2-6 ، جداول 4-6) اندازه گیریهای انجام شده از مدار در سه سطح ولتاژ: 4.3 ولت ، 3.9 ولت و 3.6 ولت است. هر سطح نمودار را نشان می دهد که تفاوت بین مقادیر ADC اندازه گیری شده و نظری را نشان می دهد. مقادیر نظری به نزدیکترین عدد صحیح گرد می شود. یک نمودار خلاصه برای مقایسه تفاوت ها در سه سطح ولتاژ وجود دارد. سپس یک نمودار وجود دارد که ارتباط بین مقادیر ADC نظری و جریان بار را در سطوح مختلف ولتاژ نشان می دهد.

نتیجه

دستگاه در سه سطح ولتاژ آزمایش شد: 3.6 ولت ، 3.9 ولت و 4.3 ولت. محدوده این ولتاژها یک باتری لیتیوم یونی کامل را مدل سازی می کند که تا سطح اسمی آن تخلیه می شود. از سه سطح ولتاژ ، مشاهده می شود که دستگاه به طور معمول در مدار 3.9 ولت برای مدار خارجی انتخابی دقیق تر بود. تفاوت بین مقادیر ADC اندازه گیری شده و نظری تنها 1 مقدار اعشاری در جریانهای بار 700 - 1000 میکرو آمپر بود. در محدوده ولتاژ داده شده ، مقادیر ADC اندازه گیری شده در بدترین حالت 3 نقطه اعشار بالاتر از شرایط اسمی بود. برای بهینه سازی سطوح مختلف ولتاژ VDD می توان تنظیمات بیشتری در تقسیم مقاومت انجام داد.

توصیه شده:

در حال حاضر نیازی به کار ندارید ، دستگاه تنظیم رفتار حیوان خانگی که گربه ها را در خانه شما متوقف می کند: 4 مرحله

No Pee Now ، دستگاه کنترل رفتار حیوان خانگی که باعث می شود گربه ها در خانه شما ادرار کنند: من آنقدر از بچه گربه ام اذیت شدم که او دوست دارد روی تختم ادرار کند ، همه چیز را که نیاز دارد بررسی کردم و او را نیز نزد دامپزشک بردم. بعد از اینکه همه چیز را که فکر می کنم و به حرف پزشک گوش می دهم برطرف کردم ، متوجه می شوم که او فقط رفتار بدی دارد. بنابراین ث

چگونه می توان با استفاده از مonلفه هایی که در حال حاضر به هرگونه مقاومت/ظرفیت دست یافته اید!: 6 مرحله

چگونه می توان با استفاده از مonلفه هایی که در حال حاضر به هرگونه مقاومت/ظرفیت دست یافته اید!: این فقط یک سری دیگر/محاسبه کننده مقاومت معادل موازی نیست! این برنامه نحوه ترکیب مقاومت ها/خازن هایی را که در حال حاضر برای دستیابی به مقاومت/ظرفیت خازنی مورد نیاز خود محاسبه می کنید ، محاسبه می کند. آیا تا به حال به مشخصات نیاز داشته اید

مدل خودکار طرح راه آهن در حال اجرا دو قطار (V2.0) - مبتنی بر آردوینو: 15 مرحله (همراه با تصاویر)

مدل خودکار طرح راه آهن در حال اجرا دو قطار (V2.0) | مبتنی بر آردوینو: خودکار طرح بندی راه آهن با استفاده از میکروکنترلرهای آردوینو راهی عالی برای ادغام میکروکنترلرها ، برنامه نویسی و مدل راه آهن در یک سرگرمی است. مجموعه ای از پروژه های موجود برای راه اندازی قطار به صورت خودکار در مدل راه آهن موجود است

نحوه ایجاد درایو بوت لینوکس (و نحوه استفاده از آن): 10 مرحله

نحوه ایجاد درایو بوت لینوکس (و نحوه استفاده از آن): این یک معرفی ساده در مورد نحوه شروع کار با لینوکس ، به ویژه اوبونتو است

موجودی - تشخیص سریع رایانه در حال حاضر جایگزین شده است ، به زیر مراجعه کنید: 6 مرحله

موجودی - تشخیص سریع رایانه در حال حاضر جایگزین شده است ، به زیر مراجعه کنید: اگر تا به حال نیاز به کار بر روی رایانه ای دارید که در جلوی شما نیست ، به یک موجودی دقیق نیاز دارید. این دستورالعمل صرفاً به این دلیل ایجاد شد که یک همکار در پیدا کردن راننده برای رایانه مشکل دارد. من از Aida32 شخصی از http://majorgeeks.com استفاده خواهم کرد