فهرست مطالب:

- تدارکات

- مرحله 1: Gerber را به سازنده Pcb دلخواه خود آپلود کنید

- مرحله 2: مجمع هیئت مدیره

- مرحله 3: راه اندازی نرم افزار

تصویری: Mojo FPGA Board Board Shield: 3 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:53

با استفاده از این سپر ، برد توسعه Mojo خود را به ورودی های خارجی وصل کنید.

برد توسعه Mojo چیست؟

هیئت توسعه Mojo یک تخته توسعه است که در اطراف Xilinx spartan 3 FPGA قرار دارد. تخته توسط Alchitry ساخته شده است. FPGA در مواردی که چندین فرآیند باید به طور همزمان اجرا شوند بسیار مفید هستند.

به چه چیزی نیاز خواهید داشت؟

تدارکات

تابلوی توسعه موجو

پرونده Gerber

مقاومت 8 x 15k اهم (اختیاری*)

4 مقاومت 470 اهم

4 مقاومت 560 اهم

4 x CC صفحه نمایش هفت بخش

LED های 4 * 3 میلی متر

4 عدد سوئیچ لمسی SPDT

سوئیچ DIP سطح نصب 1 در 4

2 * 25 در 2 یا 4 * 25 سرصفحه

سر جعبه 1x2 در 5 پین

آهن لحیم کاری

لحیم کاری

هجوم

*(در صورت حذف این مقاومتها ، کشش/کشش داخلی باید برای پینهای مربوطه فعال باشد)

مرحله 1: Gerber را به سازنده Pcb دلخواه خود آپلود کنید

برای تخته های خود از JLC PCB سفارش دادم.

تنها تغییری که ایجاد کردم رنگی بود که می خواستم با رنگ مشکی موجو مطابقت داشته باشد.

مرحله 2: مجمع هیئت مدیره

هنگام لحیم کاری ، همیشه لحیم کردن پایین ترین قطعات مفید است ، بنابراین شروع با مقاومت ها ایده خوبی است.

R5 ، R6 ، R7 ، R8 ، R9 ، R10 ، R11 و R12 مقاومت های 15k اهم هستند که برای پایین کشیدن سوئیچ ها استفاده می شوند (اگر از کشش داخلی/کشش داخلی استفاده می کنید این مورد را نادیده بگیرید).

R1 ، R2 ، R3 ، R4 مقاومتهای 560 اهم هستند که وظیفه محدود کردن جریان از طریق صفحه نمایش 7 قسمتی را بر عهده دارند.

R13 ، R14 ، R15 ، R16 مقاومت 470 اهم هستند که وظیفه محدود کردن جریان از طریق 4 LED را بر عهده دارند.

در مرحله بعد کلید سوئیچ ، کلیدهای لمسی ، LED ها ، نمایشگرهای هفت قسمتی و کانکتور header box را به آن ترتیب لحیم کنید.

حالا 25 را در 2 (یا 2 25 در 1) در موجو قرار دهید تا پین ها تراز شوند. سپر را با پین ها تراز کرده و در جای خود لحیم کنید.

مرحله 3: راه اندازی نرم افزار

برای نرم افزاری که به وب سایت Alchitry مراجعه می کند ، به شما اطلاع می دهد که برای شروع و نصب Xilinx ISE به چه چیزی نیاز دارید. با این حال ، فایل.ucf را تغییر دهید تا بداند کدام پین ها به آنچه برای اجرای برنامه شما مهم است متصل شده اند.

در اینجا فایل.ucf است که با سپر استفاده می کنم:

پیکربندی VCCAUX = 3.3 ؛

NET "clk" TNM_NET = clk؛ TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50٪؛ NET "clk" LOC = P56 | IOSTANDARD = LVTTL ؛ NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL ؛ NET "cclk" LOC = P70 | IOSTANDARD = LVTTL ؛ NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL ؛ NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL ؛ NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL ؛ NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL ؛ NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL ؛ NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL ؛ NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL ؛ NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL ؛ NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL ؛ NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL ؛ NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL ؛ NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL ؛ NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL ؛ NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL ؛ NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL ؛ NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL ؛ NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL ؛ NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL ؛ NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL ؛ NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL ؛ NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL ؛ NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL ؛ NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL ؛ NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL ؛ NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL ؛ NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL ؛ NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL ؛ NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL ؛ NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL ؛ NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL ؛ NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL ؛ NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL ؛ NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL ؛ NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL ؛ NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL ؛ NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL ؛ NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL ؛ NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL ؛ NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL ؛ NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL ؛ NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL ؛ NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL ؛ NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL ؛ NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL ؛ NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL ؛ NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL ؛ NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL ؛ NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL ؛ NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL ؛ NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL ؛ NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL ؛ NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL ؛ NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL ؛ NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL ؛ NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL ؛

به یاد داشته باشید که اگر مقاومت های کشویی را برای ویرایش پین ها در.ucf با نصب نکرده اید

| پایین کشیدن؛ o

| PULLUP ؛

اگر می خواهید از بلوک برای هر چیزی استفاده کنید ، اتصالات به شرح زیر است. در سمت چپ شماره پین بلوک و راست شماره پین mojo است که باید در.ucf خود تعیین کنید:

پین 1 = 29

پین 2 = 51

پین 3 = 32

پین 4 = 41

پین 5 = 34

پین 6 = 35

پین 7 = 40

پین 8 = 33

پین 9 = GND

پین 10 = +V

توصیه شده:

FPGA Cyclone IV DueProLogic دوربین رزبری پای را کنترل می کند: 5 مرحله

FPGA Cyclone IV DueProLogic دوربین رزبری پای را کنترل می کند: با وجود اینکه FPGA DueProLogic به طور رسمی برای آردوینو طراحی شده است ، ما FPGA و Raspberry Pi 4B را قابل انتقال می کنیم. سه کار در این آموزش اجرا می شود: (الف) همزمان دو دکمه را فشار دهید FPGA برای چرخاندن زاویه

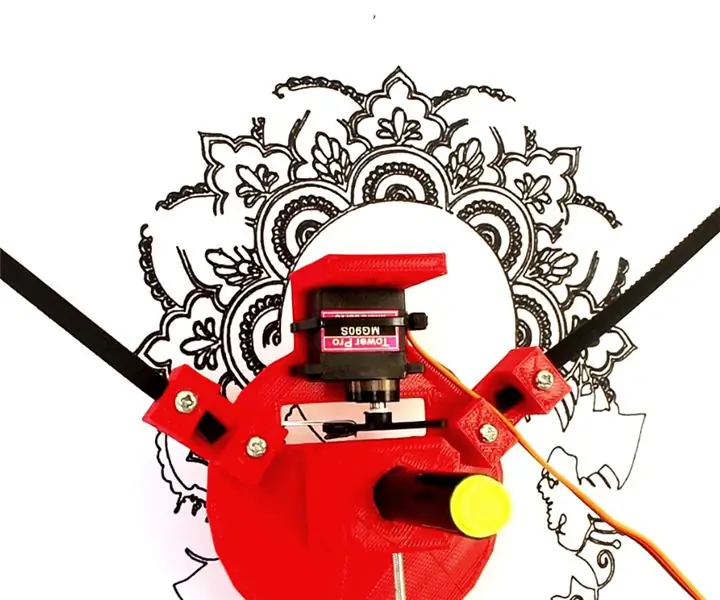

MXY Board - کم هزینه بود XY Plotter Drawing Robot Board: 8 مرحله (همراه با تصاویر)

تخته MXY - روبات تابلوی نقاشی XY Plotter با بودجه کم: هدف من این بود که تخته mXY را طراحی کنم تا با هزینه کم دستگاه نقشه کشی XY را طراحی کنم. بنابراین من یک تخته طراحی کردم که کار را برای کسانی که می خواهند این پروژه را راحت تر کنند راحت تر می کند. در پروژه قبلی ، هنگام استفاده از 2 عدد موتور پله ای Nema17 ، این برد شما

انجام بازی Flappy Bird Game with M5stack Esp32 Based M5stick C Board Board: 5 مرحله

بازی Flappy Bird Game With M5stack Esp32 Based M5stick C Board: سلام بچه ها امروز ما یاد می گیریم که چگونه کد بازی flappy bird را در تخته توسعه m5stick c ارائه شده توسط m5stack بارگذاری کنیم. برای این پروژه کوچک به دو مورد نیاز دارید: m5stick-c هیئت توسعه: https://www.utsource.net/itm/p/8663561.h

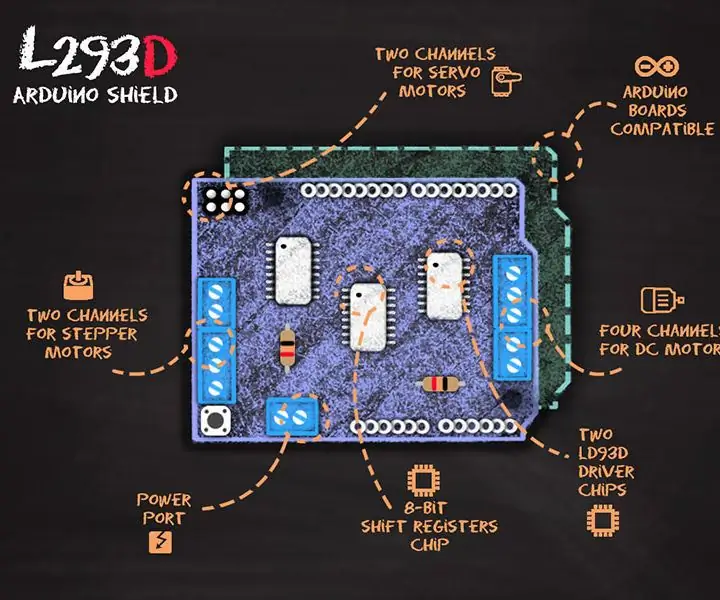

آموزش Arduino L293D Motor Shield Shield: 8 مرحله

Arduino L293D Motor Driver Shield Tutorial: می توانید این و بسیاری از آموزش های شگفت انگیز دیگر را در وب سایت رسمی ElectroPeak بخوانید. مرور کلی در این آموزش ، نحوه رانندگی DC ، پله ای و سروو موتور با استفاده از سپر درایور موتور Arduino L293D را خواهید آموخت. آنچه خواهید آموخت:

Arduino Uno: Bitmap Animation در ILI9341 TFT Touchscreen Shield Shield With Visuino: 12 مرحله (همراه با تصاویر)

Arduino Uno: Bitmap Animation on ILI9341 TFT Touchscreen Shield With Visuino: Shield های صفحه نمایش TFT مبتنی بر TFT مبتنی بر ILI9341 بسیار محبوب هستند. Visuino مدتی است که از آنها پشتیبانی می کند ، اما من هرگز فرصتی برای نوشتن یک آموزش در مورد نحوه استفاده از آنها نداشتم. اما اخیراً تعداد کمی از افراد پرسیدند