فهرست مطالب:

- مرحله 1: Vivado HLS چیست؟

- مرحله 2: کتابخانه ویدیویی HLS

- مرحله 3: سنتز

- مرحله 4: نسخه بندی و سایر اطلاعات برای صادرات

- مرحله 5: صادرات به کتابخانه IP Vivado

- مرحله 6: سنتز و تجزیه و تحلیل صادرات

- مرحله 7: افزودن کتابخانه IP در Vivado

- مرحله 8: انجام ارتقاء

- مرحله 9: جزئیات و اطلاعات بیشتر

- مرحله 10: خروجی و ورودی

- مرحله 11: رابط AXI را ثبت کنید

- مرحله 12: Dataflow Pragma

تصویری: Vivado HLS Video IP Block Synthesis: 12 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:57

آیا تا به حال خواسته اید بدون افزودن تأخیر زیاد یا در یک سیستم جاسازی شده ، ویدئو را در زمان واقعی پردازش کنید؟ گاهی اوقات از FPGA (آرایه های دروازه ای قابل برنامه ریزی) برای این کار استفاده می شود. با این حال ، نوشتن الگوریتم های پردازش ویدیو در زبان های سخت افزاری مانند VHDL یا Verilog در بهترین حالت ناامید کننده است. Vivado HLS را وارد کنید ، ابزار Xilinx که به شما امکان می دهد در محیط C ++ برنامه نویسی کرده و کد زبان سخت افزار را از آن ایجاد کنید.

نرم افزارهای مورد نیاز:

- Vivado HLS

- ویوادو

- (اگر از رجیسترهای AXI استفاده می کنید) Vivado SDK

(اختیاری) نمونه های ساخته شده از Xilinx را در اینجا بارگیری کنید:

نمونه های ویدیویی Xilinx HLS

مرحله 1: Vivado HLS چیست؟

Vivado HLS ابزاری است که برای تبدیل کد شبیه c ++ به ساختارهای سخت افزاری قابل اجرا بر روی FPGA استفاده می شود. این برنامه شامل IDE برای انجام این توسعه می باشد. پس از تکمیل توسعه کد برای HLS ، می توانید IP تولید شده خود را در قالب صادر کنید برای استفاده با Vivado

فایلهای پیوست را بارگیری کرده و آنها را در جایی که پروژه خود را ایجاد می کنید قرار دهید. (اگر نام تصادفی دارند آنها را به "top.cpp" و "top.h" تغییر دهید)

مرحله 2: کتابخانه ویدیویی HLS

کتابخانه ویدیویی HLS دارای اسناد و مدارک با طرحهای مرجع در این مقاله است: XAPP1167 یکی دیگر از منابع خوب صفحه Xilinx Wiki در مورد آن است.

Vivado HLS را راه اندازی کنید.

ایجاد یک پروژه جدید

فایلهایی را که در مرحله قبل بارگیری کرده اید بردارید و آنها را به عنوان فایل منبع اضافه کنید. (توجه: فایل ها در پروژه کپی نمی شوند ، اما در عوض در همان جایی که هستند باقی می مانند)

سپس از دکمه Browse برای انتخاب عملکرد بالا استفاده کنید.

در صفحه بعد ، قسمت Xilinx را که استفاده می کنید انتخاب کنید.

مرحله 3: سنتز

راه حل => اجرای C Synthesis => راه حل فعال

پس از 227.218 ثانیه ، باید انجام شود. (توجه: زمان واقعی سنتز شما بر اساس عوامل زیادی متفاوت خواهد بود)

مرحله 4: نسخه بندی و سایر اطلاعات برای صادرات

شماره های نسخه با Vivado ارتباط برقرار می کنند تا بتوانید IP را در طراحی به روز کنید. اگر یک تغییر جزئی باشد ، می توان آن را در محل انجام داد در حالی که تغییرات عمده نسخه شما را ملزم می کند که بلوک جدید را به صورت دستی اضافه کرده و بلوک قدیمی را حذف کنید. اگر رابط های شما تغییر نکرده اند و به روز رسانی نسخه جزئی است ، به روز رسانی می تواند به طور خودکار با فشار دادن دکمه IP به روز رسانی انجام می شود. برای مشاهده وضعیت IP خود می توانید "report_ip_status" را در کنسول Vivado tcl اجرا کنید.

شماره نسخه و سایر اطلاعات را در Solution => Solution Settings تنظیم کنید…

متناوبا ، این تنظیمات را می توان در حین صادرات تنظیم کرد.

مرحله 5: صادرات به کتابخانه IP Vivado

راه حل => صادرات RTL

اگر جزئیات کتابخانه IP را در مرحله قبل تنظیم نکرده اید ، اکنون می توانید این کار را انجام دهید.

مرحله 6: سنتز و تجزیه و تحلیل صادرات

در این صفحه می توان آمار مربوط به ماژول صادر شده خود را مشاهده کرد که نشان می دهد با ساعت 10 نانوس (100 مگاهرتز) و میزان استفاده از هر منبع مطابقت دارد.

با ترکیبی از این ، گزارش تجزیه و تحلیل جریان داده و داده های ما ، می توانیم ببینیم که 317338 چرخه ساعت * مدت زمان 10ns * 14 مرحله خط لوله = 0.04442732 ثانیه طول می کشد. به این معنی که کل تأخیر اضافه شده توسط پردازش تصویر ما کمتر از یک بیستم ثانیه است (هنگامی که در 100 مگاهرتز مورد نظر تعیین می شود).

مرحله 7: افزودن کتابخانه IP در Vivado

برای استفاده از بلوک IP سنتز شده خود ، باید آن را به Vivado اضافه کنید.

در Vivado با رفتن به کاتالوگ IP یک مخزن IP به پروژه خود اضافه کنید و روی "افزودن مخزن …" راست کلیک کنید.

به فهرست پروژه Vivado HLS خود بروید و فهرست راه حل خود را انتخاب کنید.

باید IP ای را که پیدا کرده گزارش کند.

مرحله 8: انجام ارتقاء

گاهی اوقات لازم است بلاک HLS خود را پس از گنجاندن آن در طرح Vivado تغییر دهید.

برای انجام این کار ، می توانید تغییرات را اعمال کرده و IP را مجدداً سنتز کرده و با شماره نسخه بالاتر صادر کنید (در مورد تغییرات عمده و جزئی نسخه اصلی جزئیات را در مرحله قبل ببینید).

پس از تغییر صادرات نسخه جدید ، مخازن IP خود را در Vivado تازه کنید. این کار را می توان زمانی انجام داد که Vivado متوجه شد که IP در مخزن تغییر کرده است یا به صورت دستی فعال شده است. (توجه داشته باشید ، اگر مخازن IP خود را پس از شروع به روز کنید ، اما قبل از اتمام صادرات در HLS ، IP به طور موقت وجود نخواهد داشت ، منتظر بمانید تا به پایان برسد و دوباره بازخوانی شود.)

در این مرحله یک پنجره با اطلاعاتی که IP روی دیسک تغییر کرده است ظاهر می شود و به شما این امکان را می دهد که آن را با دکمه "Upgrade Selected" به روز کنید. اگر تغییر یک تغییر جزئی بوده و هیچ یک از رابط ها تغییر نکرده است ، سپس با فشار دادن آن دکمه به طور خودکار IP قبلی با IP جدید جایگزین می شود ، در غیر این صورت ممکن است به کار بیشتری نیاز باشد.

مرحله 9: جزئیات و اطلاعات بیشتر

مراحل زیر اطلاعات بیشتری در مورد نحوه عملکرد سنتز HLS و کارهایی که می توانید با آن انجام دهید ارائه می دهد.

برای نمونه پروژه ای که از بلوک IP سنتز شده HLS استفاده می کند ، این مورد قابل مشاهده را ببینید.

مرحله 10: خروجی و ورودی

خروجی ها و ورودی ها به بلوک IP نهایی از تجزیه و تحلیل سنتز کننده جریان داده ها به داخل و خارج از عملکرد بالا تعیین می شود.

مشابه VHDL یا verilog ، HLS به شما امکان می دهد جزئیات مربوط به اتصالات بین IP را مشخص کنید. این سطرها نمونه هایی از این موارد هستند:

فیلتر تصویری باطل (AXI_STREAM & video_in ، AXI_STREAM & video_out ، int & x ، int & y) {

#pragma HLS INTERFACE port port = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE port port = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = bundle = CONTROL_BLUSB_FUS = 0

می توانید ببینید که چگونه پورت های نمایش داده شده در بلوک IP تحت تأثیر این دستورالعمل ها قرار می گیرند.

مرحله 11: رابط AXI را ثبت کنید

برای دریافت ورودی/خروجی به/از بلوک IP خود به PS راه خوبی برای این کار از طریق رابط AXI است.

می توانید این را در کد HLS خود مشخص کنید ، از جمله offsets هایی که بعداً برای دسترسی به مقدار استفاده می شود:

فیلتر تصویری باطل (AXI_STREAM & video_in ، AXI_STREAM & video_out ، int & x ، int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42 ؛

y = 0xDEADBEEF ؛ }

پس از اتصال صحیح در Vivado ، می توانید با استفاده از این کد در Vivado SDK به مقادیر دسترسی پیدا کنید:

#شامل "paramet.h"

#xregoff 0x14 #تعریف yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff) ؛ y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff) ؛

با این کار 42 در x و 0xdeadbeef در y به دست می آورید

مرحله 12: Dataflow Pragma

در داخل #pragma DATAFLOW نحوه اجرای کد از C ++ معمولی تغییر می کند. کد به گونه ای خط لوله شده است که همه دستورالعمل ها در هر زمان در قسمت های مختلف داده اجرا می شوند (مانند خط مونتاژ در کارخانه فکر کنید ، هر ایستگاه به طور مداوم در حال انجام یک عملکرد است و آن را به ایستگاه بعدی منتقل می کند)

از تصویر می توانید ببینید که هر یک از دستورالعمل ها

با وجود اینکه متغیرهای معمولی به نظر می رسند ، اما اشیاء img در واقع به عنوان بافرهای کوچک بین دستورات پیاده سازی می شوند. استفاده از یک تصویر به عنوان ورودی یک تابع آن را "مصرف" می کند و دیگر قابل استفاده نیست. (بنابراین نیاز به دستورات تکراری است)

توصیه شده:

اسپکتروفتومتر بلوک Jenga Block برای آزمایش جلبک: 15 مرحله

اسپکتروفتومتر بلوک Jenga Block برای آزمایش جلبک ها: جلبک ها پروتئوس های اولیه فتوسنتز هستند و به همین ترتیب ، موجودات حیاتی در زنجیره های غذایی آبزیان هستند. با این حال ، در ماههای بهار و تابستان ، این میکروارگانیسمها و سایر میکروارگانیسمها می توانند منابع طبیعی آب را تکثیر کرده و تحت فشار قرار دهند و در نتیجه اکسیژن کم شود

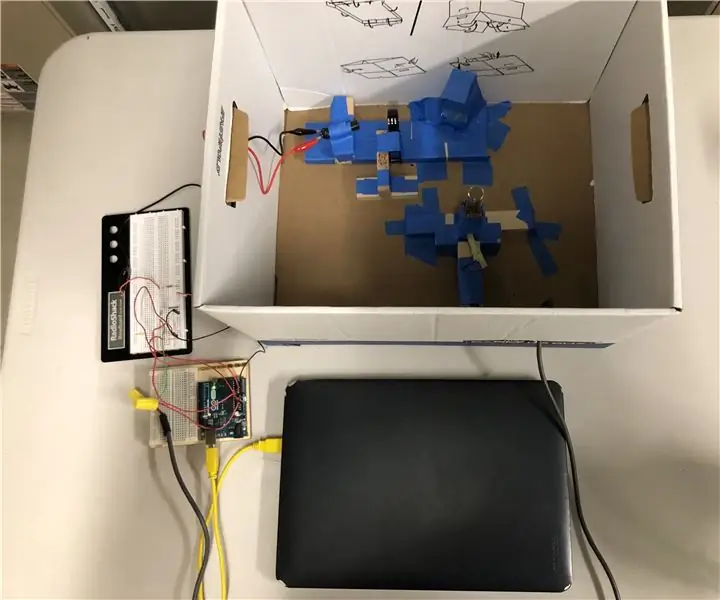

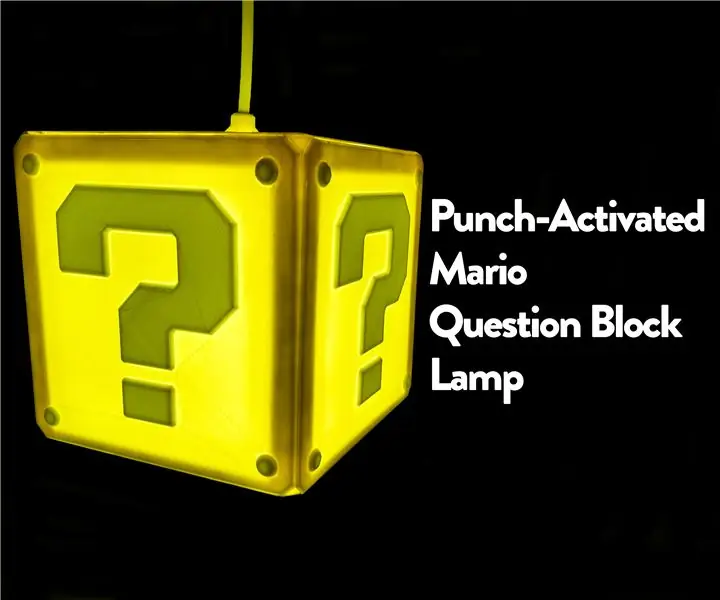

Punch Activated Mario Question Block Lamp: 8 مرحله (همراه با تصاویر)

Punch Activated Mario Question Block Lamp: بازی های سوپر ماریو دوران کودکی من بود. من همیشه می خواستم برخی از وسایل بازی را در اختیار داشته باشم ، و اکنون که ابزارهایی برای انجام این کار دارم ، تصمیم گرفتم ساخت آنها را شروع کنم. اولین موردی که در لیست من وجود دارد بلوک سionالات است. من موفق شدم

IOT123 - D1M BLOCK - 2xAMUX مونتاژ: 7 مرحله (همراه با تصاویر)

IOT123 - D1M BLOCK - 2xAMUX مونتاژ: D1M BLOCKS موارد لمسی ، برچسب ها ، راهنماهای قطبی و شکست ها را برای WEMOS D1 Mini SOC/Shields/Clones محبوب اضافه می کند. یکی از مشکلات تراشه ESP8266 این است که تنها یک پین IO آنالوگ در دسترس است. این دستورالعمل نحوه مونتاژ 2xA را نشان می دهد

نحوه استفاده از Vivado Simluation: 6 مرحله

نحوه استفاده از شبیه سازی Vivado: من این پروژه شبیه سازی را برای یک کلاس آنلاین انجام داده ام. پروژه توسط Verilog نوشته شده است. ما از شبیه سازی در Vivado برای تجسم شکل موج در enable_sr (فعال کردن رقم) از پروژه stop watch که قبلاً ایجاد شده است ، استفاده خواهیم کرد. علاوه بر این ، ما به ما

Toddler Video Remote for PC Video Player: 6 مرحله

Toddler Video Remote for PC Video Player: من یک کنترل از راه دور ایجاد می کنم که با USB به کامپیوتر متصل می شود. کنترل از راه دور بزرگ به کودک نوپا اجازه می دهد فیلم ها را در رایانه قدیمی انتخاب و پخش کند. این یک پروژه نسبتاً ساده است. جزء اصلی یا صفحه کلید USB یا صفحه کلید USB بی سیم است. سپس