فهرست مطالب:

- مرحله 1: ایجاد ماژول PWM- منبع فایل

- مرحله 2: ایجاد ماژول PWM- راه اندازی Vivado

- مرحله 3: ایجاد یک ماژول PWM- ایجاد یک پروژه پروژه

- مرحله 4: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (I)

- مرحله 5: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (II)

- مرحله 6: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (III)

- مرحله 7: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (IV)

- مرحله 8: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (V)

- مرحله 9: ساخت ماژول PWM- نصب سخت افزار

- مرحله 10: ایجاد یک ماژول PWM- ایجاد Bitstream و راه اندازی SDK

- مرحله 11: ایجاد یک ماژول PWM- ایجاد یک برنامه جدید در Xilinx SDK

- مرحله 12: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (I)

- مرحله 13: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (II)

- مرحله 14: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (III)

- مرحله 15: ایجاد یک ماژول PWM- تابع PWM (I) را جمع کنید

- مرحله 16: ایجاد یک ماژول PWM- جمع آوری عملکرد PWM (II)

- مرحله 17: ایجاد یک ماژول PWM- جمع آوری عملکرد PWM (III)

- مرحله 18: ساخت ماژول PWM- آن را اجرا کنید

- مرحله 19: جریان پردازش ویدیو در Digilent ZYBO با OV7670

- مرحله 20: نمودار بلوک را کامل کنید

- مرحله 21: OV7670 را به ZYBO وصل کنید

- مرحله 22: ایجاد طرح بلوک

- مرحله 23: فایلهای VHDL را برای کنترل و ضبط دوربین OV7670 اضافه کنید

- مرحله 24: فایل محدودیت ها را اضافه کنید

- مرحله 25: IP Repo را برای HLS IP اضافه کنید

- مرحله 26: ماژول ها و IP را اضافه کنید

- مرحله 27: تنظیمات پیکربندی IP

- مرحله 28: PS IP Block را اضافه و پیکربندی کنید

- مرحله 29: قسمت 1. ساخت ماژول PWM برای سرو موتورها

- مرحله 30: اتصالات جانبی ورودی ویدئو (برجسته aclk)

- مرحله 31: اتصال به OV7670

- مرحله 32: اتصالات در خارج از ویدئو

- مرحله 33: Block and Connection Automation را اجرا کنید

- مرحله 34: ایجاد HDL Wrapper

- مرحله 35: ایجاد Bitstream ، صادرات سخت افزار به SDK ، راه اندازی SDK از Vivado

- مرحله 36: SDK (بدون FreeRTOS)

- مرحله 37: پیاده سازی FreeRTOS

- مرحله 38: دستورالعمل استفاده

- مرحله 39: منابع و پیوندها

تصویری: دوربین ZYBO OV7670 با کنترل پنل/شیب: 39 مرحله (همراه با تصاویر)

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:57

برای ایجاد جزئیات در مورد ایجاد کنترل کننده سروو PWM دو محوره ، از مرحله یک شروع کنید.

برای بلوک دیاگرام عظیم (مرحله 19) برای پروژه کامل شروع کنید.

تنظیم دوربین + پان/شیب مورد استفاده ما:

PmodCON3 از Digilent برای اتصال سرویس ها استفاده شد.

مرحله 1: ایجاد ماژول PWM- منبع فایل

مرحله 2: ایجاد ماژول PWM- راه اندازی Vivado

ابتدا ، Vivado Design Suite را از وب سایت Xilinx بارگیری کنید. همه مجموعه طراحی ، از جمله Vivado Software Development Kit (SDK) را نصب کنید. این پروژه از نسخه 2017.2 استفاده می کند.

در ضمن ، Digilent Adept 2 نیز باید به عنوان درایور برد Zybo نصب شود.

مرحله 3: ایجاد یک ماژول PWM- ایجاد یک پروژه پروژه

قبل از ایجاد یک فایل پروژه ، باید اطمینان حاصل کنید که قبلاً فایل Zybo را به درستی به عنوان آموزش اینجا نصب کرده اید:

Vivado نسخه 2015.1 و بعد از آن نصب فایل هیئت مدیره

Vivado 2017.2 را باز کنید در شروع سریع ، روی ایجاد پروژه -> بعدی -> نام پروژه (نام پروژه خود را در اینجا نام ببرید) -> نوع پروژه کلیک کنید. در نوع پروژه ، RTL Project را انتخاب کنید و روی "در حال حاضر منابع را مشخص نکنید" علامت بزنید. بعد ، برای قسمت پیش فرض ، "Boards" و "Zybo" را به عنوان نام نمایش انتخاب کنید. بعد ، روی Finish کلیک کنید تا پروژه شروع شود.

مرحله 4: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (I)

در Flow Navigator ، روی “” Create Block Design”کلیک کنید ، سپس OK را فشار دهید. برای افزودن IP های لازم روی علامت "+" کلیک کنید. اضافه کردن:

- یک سیستم پردازش ZYNQ7 دو تایمر AXI

- دو تایمر AXI

مرحله 5: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (II)

پس از افزودن IP ها ، Block Automation و اتوماسیون اتصال را اجرا کنید. پس از اتمام اتوماسیون ، در بلوک "axi_timer_0" ، روی pwm0 -> Make External راست کلیک کنید. پین خارجی pwm0 را به عنوان pwm_Xaxis نامگذاری کنید. همچنین ، مراحل بالا را در بلوک "axi_timer_1" تکرار کنید و پین خارجی pwm0 را به عنوان pwm_Zaxis نامگذاری کنید.

مرحله 6: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (III)

توجه داشته باشید که هر زمان که Block Design را در Vivado به پایان می بریم ، باید یک HDL Wrapper ایجاد کنیم. از آنجا که ماژول سطح بالا برای هر پروژه خواهد بود.

مرحله 7: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (IV)

اکنون ، ما باید فایل محدودیت خود را برای اختصاص پین های متصل به بلوک دیاگرام خود تنظیم کنیم. پنجره Block Design را ببندید ، در برگه منابع ، "افزودن منابع"-> افزودن یا ایجاد محدودیت-> اضافه کردن Zybo-Master.xdc به عنوان فایلهای محدودیت ما.

مرحله 8: ایجاد یک ماژول PWM- طراحی بلوک و تنظیم فایل محدودیت (V)

فایل محدودیت Zybo-Master.xdc را از پوشه Constraints باز کنید ، پورت هایی را که می خواهیم به عنوان سیگنال خروجی مشخص کنیم ، کامنت گذاری کرده و نام "get_ports {XXXX}" را تغییر دهید ، که XXXX نشان دهنده پین خارجی است که در نمودار بلوک نامگذاری شده است. تنظیم فایل محدودیت در شکل نشان داده شده است.

مرحله 9: ساخت ماژول PWM- نصب سخت افزار

سرو موتورها را به Pmod CON3 وصل کنید. TowerPro SG90 مدل سرو موتور است که در این پروژه استفاده کردیم. برای سیم های سرو موتور ، سیم نارنجی نشان دهنده سیگنال PWM است که در Pmod CON3 به پین SIG متصل شده است. سیم قرمز Vcc یک سیم برق است که در Pmod CON3 به پین VS متصل شده است. در نهایت ، سیم قهوه ای Gnd یک سیم زمینی است که به پین GND متصل است. سپس ، Pmod CON3 را در ردیف بالای درگاه JD در Zybo Board وارد کنید.

مرحله 10: ایجاد یک ماژول PWM- ایجاد Bitstream و راه اندازی SDK

1. در برگه Project Navigator ، Generate BitStream را اجرا کنید.

2. صادرات سخت افزار: فایل> صادرات> صادرات سخت افزار-> علامت "شامل بیت استریم"-> OK 3. راه اندازی SDK: فایل-> راه اندازی SDK.

مرحله 11: ایجاد یک ماژول PWM- ایجاد یک برنامه جدید در Xilinx SDK

ایجاد یک برنامه جدید:

فایل> جدید> پروژه برنامه -> نام پروژه خود را وارد کنید -> پایان

تحت Project Explorer ، باید سه پوشه وجود داشته باشد.

در این مورد ، "design_1_wrapper_hw_platform_0" پوشه ای است که قبلاً توسط Vivado صادر شده است. Axis_2_PWM_SDK_bsp پوشه بسته پشتیبانی برد است. و Axis_2_PWM_SDK پوشه اصلی پروژه ما در SDK است. می توانید فایل "helloworld.c" را در زیر پوشه "src" Axis_2_PWM_SDK مشاهده کنید ، جایی که "helloworld.c" فایل اصلی است.

مرحله 12: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (I)

بیایید برخی از فایل ها را تحت Project Explorer بررسی کنیم. ابتدا ، در پوشه "design_1_wrapper_hw_platform_0" ، "system.hdf" را باز کنید. این فایل نقشه آدرس پردازنده ps7_cortex9 و بلوک های IP موجود در طراحی ما را نشان می دهد.

مرحله 13: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (II)

سپس ، فایل "include" و "libsrc" را در پوشه "Axis_2_PWM_SDK_bsp" بررسی کنید. فایلهای کتابخانه در اینجا ما را قادر می سازد تا با تجهیزات جانبی سخت افزاری بدون ثبت "پخش" تعامل داشته باشیم.

مرحله 14: ایجاد یک ماژول PWM- نمای کلی از Explorer Project (III)

از طریق اسناد BSP ، xtmrctr.h به عنوان کتابخانه کنترل تایمر Xilinx مربوط به AXI Timer یافت می شود. به طور معمول ، ما می توانیم تابع PWM مورد نظر را در اینجا پیدا کنیم. با این حال ، اگر اسناد "tmrctr_v4_3" را بخوانید ، نشان می دهد که درایور در حال حاضر از عملکرد PWM دستگاه پشتیبانی نمی کند. به دلیل نقص در عملکرد PWM ، ما باید عملکرد PWM خود را با کمک xtmrctr.h و AXI Timer v2.0 LogiCORE IP Product Guide به پایان برسانیم.

مرحله 15: ایجاد یک ماژول PWM- تابع PWM (I) را جمع کنید

به فایل اصلی "helloworld.c" برگردید ، فایلهای سرصفحه زیر را وارد کنید:

مرحله 16: ایجاد یک ماژول PWM- جمع آوری عملکرد PWM (II)

آدرس های اصلی دو AXI TImer را از طریق “xparameters.h” تعریف کنید.

مرحله 17: ایجاد یک ماژول PWM- جمع آوری عملکرد PWM (III)

عملکرد PWM مورد نظر را بسازید.

Duty_val: مقدار درجه را به چرخه وظیفه تبدیل می کند. PWM_Freq_Duty: فرکانس و چرخه وظیفه مورد نظر را برای تولید PWM تنظیم کنید. دوره ساعت نیز باید اختصاص داده شود.

PWM_START: آدرس ثبت PWM را تعیین کرده و تولید PWM را آغاز کنید.

PWM_STOP: آدرس ثبت PWM را تعیین کرده و تولید PWM را متوقف کنید.

بقیه کد نمایشی در "helloworld.c" در زیر "Axis_2_PWM_SDK" نشان داده شده است

مرحله 18: ساخت ماژول PWM- آن را اجرا کنید

1. FPGA را از طریق SDK برنامه ریزی کنید

- Zybo Board را از طریق پورت USB به رایانه وصل کنید.

- ابزارهای Xilinx -> برنامه FPGA

2. برنامه را اجرا کنید

بر روی نماد "Run" کلیک کرده و منو را رها کنید -> Run As -> Launch on Hardware

3. ترمینال SDK

- ترمینال SDK را باز کنید -> اتصال به پورت سریال -> OK

- برنامه را اجرا کنید. اگر کد نمایشی با موفقیت اجرا شد ، باید "Initialization done!" در ترمینال SDK

مرحله 19: جریان پردازش ویدیو در Digilent ZYBO با OV7670

فایل بایگانی کامل پیوست شده است.

مرحله 20: نمودار بلوک را کامل کنید

این نمودار کامل تمام اتصالات و بلوک های IP در پروژه را نشان می دهد

مرحله 21: OV7670 را به ZYBO وصل کنید

یک اتصال برای اتصال ماژول ov7670 به ZYBO Pmods ایجاد کنید

Data Pmod Pmod D است

کنترل Pmod Pmod C است

علاوه بر این ، PmodCON3 و servos را همانطور که در نیمه اول این آموزش مشخص شده است ، وصل کنید

مرحله 22: ایجاد طرح بلوک

در Flow Navigator ، روی "ایجاد طرح بلوک" کلیک کنید ، سپس OK را فشار دهید.

مرحله 23: فایلهای VHDL را برای کنترل و ضبط دوربین OV7670 اضافه کنید

فایلهای VHDL متصل به این مرحله را به پروژه اضافه کنید

مرحله 24: فایل محدودیت ها را اضافه کنید

فایل محدودیت های پیوست شده را به پروژه خود اضافه کنید.

مرحله 25: IP Repo را برای HLS IP اضافه کنید

فایل Zip پیوست شده را بردارید و آن را در یک پوشه جدید با نام مشابه در یک پوشه (پوشه) جدید به نام "HLS_repo" باز کنید.

با رفتن به کاتالوگ IP ، مخزن IP را به پروژه خود اضافه کنید و روی "افزودن مخزن …" راست کلیک کنید.

به فهرست "HLS_repo" خود بروید و آن را انتخاب کنید.

اختیاری: بلاک پردازش ویدیو HLS را برای خود ایجاد کنید!

مرحله 26: ماژول ها و IP را اضافه کنید

با کلیک راست روی پس زمینه و انتخاب "افزودن ماژول …" ، ماژول های ov7670_axi_stream_capture ، debounce و ov7670_controller را به بلوک دیاگرام اضافه کنید.

به طور مشابه ، IP ها را اضافه کنید:

- HLS_Video_Track

- بافر قاب ویدیویی بنویسید

- بافر قاب ویدیویی خوانده شده است

- کنترل کننده زمان بندی ویدئو

- جریان AXI4-Out to Video Out

- 3 از "برش"

- مقدار ثابت

- 2 تایمر AXI

مرحله 27: تنظیمات پیکربندی IP

همانطور که در تصاویر نشان داده شده است

مرحله 28: PS IP Block را اضافه و پیکربندی کنید

سیستم پردازش ZYNQ7 را به نمودار بلوک اضافه کنید

پیکربندی را ویرایش کنید:

-

پیکربندی PS-PL

-

HP

- S HP 0 را فعال کنید

- S HP 1 را فعال کنید

-

-

پیکربندی ساعت

-

ساعتهای پارچه ای PL

- FCLK_0 با فرکانس 100 مگاهرتز

- FCLK_1 در 25 مگاهرتز (OutputClock)

- FLCK_2 در 35 مگاهرتز (<= 50 مگاهرتز) (CameraClock)

-

مرحله 29: قسمت 1. ساخت ماژول PWM برای سرو موتورها

axi_timer_0 pwm0 را به درگاه خروجی pwm_Xaxis جدید بیاورید

axi_timer_1 pwm0 را به درگاه خروجی جدید pwm_Zaxis بیاورید

مرحله 30: اتصالات جانبی ورودی ویدئو (برجسته aclk)

بلوک های IP سمت ورودی ویدئو را به درستی وصل کنید

(* این اتصالات باید با انتخاب گزینه های مناسب در هنگام اتوماسیون اتصال ایجاد شوند) "aclk" از axi_stream_capture به آدرس زیر می رود:

- ap_clk روی بافر فریم ویدیویی بنویسید

- ap_clk در بلوک پردازش جریان ویدیو HLS

- *پیوند IP با AXI smartconnect را از بافر فریم ویدیویی بنویسید به S_AXI_HP0

- *aclk مربوط به کانال های IP AXI Interconnect برای کانال های S_AXI بلوک پردازش ویدیو HLS و بافر فریم ویدیویی S_AXI_HP0_ACLK را روی بلوک PS بنویسید

سیگنال جریان ویدئو به سادگی به صورت سری از بلوک ضبط به رابط حافظه Zynq متصل می شود.

- ویدیو از بلوک ضبط به بلوک پردازش HLS می رود.

- فیلم پردازش شده از بلوک HLS به بلوک نوشتن بافر فریم می رود.

- *بلوک نوشتن بافر فریم به رابط HP0 در بلوک Zynq PS متصل می شود.

- سیگنال m_axis_tuser از خروجی بلوک ضبط به صورت دستی به سیگنال ورودی video_in_TUSER در بلوک پردازش HLS و سیگنال ap_start در همان بلوک متصل می شود.

سیگنال TUSER (tuser) توسط پروتکل جریان ویدئویی AXI برای نشان دادن شروع یک فریم از ویدئو استفاده می شود. AP_Start به بلوک HLS می گوید که پردازش را شروع کند. بنابراین ما از tuser برای فعال کردن بلوک HLS برای پردازش هر فریم به صورت خود استفاده می کنیم. وارد می شود. هنگام اتصال یک سیگنال واحد از یک گذرگاه و جدا کردن آن به این روش ، لازم است که آن را نقطه پایان عادی بقیه گذرگاه نیز متصل کنید. Vivado فرض می کند که اگر سیگنال را به صورت دستی وصل می کنید می خواهید آنچه معمولاً به آن متصل می شود را قطع کنید.

تنظیمات پیکربندی بلوک های IP:

بافر فریم ویدیویی بنویسید:

فرمت های ویدیویی: RGB8

1 نمونه در هر ساعت حداکثر ستون: 1280 (> = 640) حداکثر ردیف: 960 (> = 480) حداکثر عرض داده: 8

مرحله 31: اتصال به OV7670

در بلوک ov7670_axi_stream_capture

- همه ورودی ها را خارجی کنید (روی پین راست کلیک کرده و از منو انتخاب کنید ، یا کلیک چپ-> ctrl+T)

- اسامی را همانطور که هستند بگذارید

در بلوک ov7670_controller

- همه خروجی های بلوک را خارجی کنید

- پورت config_finished را به led0 تغییر نام دهید

- clk را به CameraClock وصل کنید (<= 50 مگاهرتز) (FCLK_2)

در بلوک بازپرداخت

- ورودی button1 را به یک پورت ورودی خارجی به نام btn0 وصل کنید

- out1 را به خط ارسال مجدد در بلوک IP ov7670_controller متصل کنید

- ورودی button2 را به یک پورت ورودی خارجی به نام btn3 وصل کنید

- out2n را به ورودی ext_reset_in در IP Reset System Processor برای دامنه ساعت ضبط ویدئو وصل کنید. (*این کار ممکن است پس از ایجاد IP*انجام شود)

- clk را به CameraClock وصل کنید (<= 50 مگاهرتز) (FCLK_2)

مرحله 32: اتصالات در خارج از ویدئو

اتصالات بلوک های کنترل زمان ویدئو (VTC) ، AXI4-Stream to Video Out و برش ها

- از ساعت 25 مگاهرتز (FCLK_1) برای vid_io_out_clk و VTC clk استفاده کنید

- از ساعت 100 مگاهرتز (FCLK_0) برای aclk در AXI4-Stream to Video Out استفاده کنید

- vtiming_out به vtiming_in

- ویدئو فریم بافر خواندن m_axis_video به AXI4-Stream می رود تا ویدیو خارج شود

- vtg_ce به gen_clken می رود

- VTC clken ، aclken ، vid_io_out_ce را به Constant dout وصل کنید [0: 0]

- vid_hsync و vid_vsync را به ترتیب به پورت های خروجی vga_hs و vga_vs بیاورید. (تصویر ندارد)

برش ها:

-

برش ها باید مطابق تصاویر پیوست تنظیم شوند

- نام بلوک ها را به slice_red ، slice_green و slice_blue تغییر دهید

- محدوده های برش را تنظیم کنید ، همانطور که در تصاویر به نام بلوک نشان داده شده است

- همانطور که در تصویر نشان داده شده است ، هر برش خروجی را به خروجی پورت خارجی متصل کنید.

- vid_data [23: 0] به ورودی های هر برش متصل می شود (دین [23: 0])

مرحله 33: Block and Connection Automation را اجرا کنید

Block Automation را برای اتصال موارد از بلوک ZYNQ7 PS اجرا کنید. همانطور که در تصویر نشان داده شده است.

برای ایجاد همه IP های اتصال ، اتوماسیون اتصال را اجرا کنید. به تمام گزینه های موجود در هر تصویر توجه زیادی داشته باشید.

در بلوک خروج ، out2n را به دامنه ساعت ضبط ویدئو Processor System Reset ext_reset_in ورودی وصل کنید.

مرحله 34: ایجاد HDL Wrapper

برای طراحی بلوک خود ، HDL Wrapper را ایجاد کنید.

آن را به عنوان ماژول بالا تنظیم کنید.

مرحله 35: ایجاد Bitstream ، صادرات سخت افزار به SDK ، راه اندازی SDK از Vivado

اطمینان حاصل کنید که بیت استریم را در صادرات قرار دهید.

تولید بیت استریم ممکن است زمان زیادی طول بکشد.

سپس SDK را راه اندازی کنید

مرحله 36: SDK (بدون FreeRTOS)

این نسخه همه کارها را بدون استفاده از FreeRTOS انجام می دهد و کد را به خوبی متراکم می کند.

بر اساس طراحی سخت افزار BSP مستقل ایجاد کنید. گزینه های پیش فرض باید خوب باشد. مطمئن شوید منابع BSP ایجاد شده اند.

برنامه را همانطور که در تصویر نشان داده شده ایجاد کنید. (برنامه خالی)

اصلی تولید شده را حذف کرده و فایلهای پیوست را وارد کنید.

مرحله 37: پیاده سازی FreeRTOS

این نسخه از FreeRTOS استفاده می کند. FreeRTOS901 BSP را بر اساس طراحی سخت افزار ایجاد کنید. گزینه های پیش فرض باید خوب باشد. مطمئن شوید منابع BSP ایجاد شده اند.

برنامه را همانطور که در تصویر نشان داده شده ایجاد کنید. (برنامه خالی)

اصلی تولید شده را حذف کرده و فایلهای پیوست را وارد کنید.

مرحله 38: دستورالعمل استفاده

اجرای این پروژه کمی مشکل است. مراحل را به ترتیب دنبال کنید.

اطمینان حاصل کنید که ZYBO شما هنگام بارگیری هیچ چیزی را بارگیری نمی کند. این بدان معناست که LED انجام شده نباید روشن شود. یک راه برای انجام این کار این است که jumper منبع بوت را روی JTAG تنظیم کنید.

پروژه (FreeRTOS یا نه) را که می خواهید از SDK برنامه ریزی کنید باز کنید

- ZYBO خود را روشن کنید. LED انجام شده نباید روشن شود.

- FPGA را با فایل بیت برنامه ریزی کنید. LED انجام شده باید روشن شود. Led0 نباید روشن شود.

- کد را اجرا کنید (به یاد داشته باشید که اگر این کار را انجام می دهید از نقطه شروع اولیه عبور کنید).

در این مرحله شما باید خروجی روی صفحه نمایش VGA خود دریافت کنید.

برای راه اندازی مجدد (در صورت اشکال یا هر چیزی): سریع روی دکمه PS-SRST ضربه بزنید یا ZYBO را خاموش کرده و سپس دوباره روشن کنید. از مرحله 2 ادامه دهید

توقف پردازنده با اشکال زدایی باعث می شود دوربین به جای حرکت ثابت بماند. جریان ویدیو به هر حال ادامه خواهد داشت.

مرحله 39: منابع و پیوندها

راهنمای مرجع و مستندات Xilinx:

- PG044 - AXI -Stream to Video Out

- PG278 - بافر فریم ویدیویی خواندن/نوشتن

پیوندهای دیگر:

- وبلاگ لائوری - ورودی VDMA

- وبلاگ لائوری - خروجی OV7670 به VGA با استفاده از BRAM

- ویکی Hamsterworks ، توسط مایک فیلدز ، منبع اصلی کد OV7670

- برگه اطلاعاتی که مشخصات اولیه زمان بندی را نشان می دهد

توصیه شده:

کنترل پنل ناسا برای کودکان: 10 مرحله (همراه با تصاویر)

کنترل پنل ناسا برای کودکان: من این را برای خواهر شوهرم ساخته ام که مراقبت روزانه دارد. او لایگر من را که تقریباً سه سال پیش برای یک شرکت سازنده ساخته بودم ، دید و واقعاً دوست داشت ، بنابراین این را برای او برای هدیه کریسمس ساختم. به پروژه دیگر من در اینجا پیوند دهید: https: //www

دیوار نصب برای IPad به عنوان کنترل پنل اتوماسیون خانگی ، با استفاده از آهنربای کنترل شده سروو برای فعال کردن صفحه: 4 مرحله (همراه با تصاویر)

دیوار نصب برای IPad به عنوان کنترل پنل اتوماسیون خانگی ، با استفاده از آهنربای کنترل شده سروو برای فعال کردن صفحه: اخیراً من زمان زیادی را صرف خودکارسازی وسایل داخل و اطراف خانه ام کرده ام. من از Domoticz به عنوان برنامه اتوماسیون خانگی خود استفاده می کنم ، برای جزئیات به www.domoticz.com مراجعه کنید. در جستجوی یک برنامه داشبورد که تمام اطلاعات Domoticz را نشان می دهد

کنترل پنل سفینه - اسباب بازی آردوینو برش لیزری: 11 مرحله (همراه با تصاویر)

کنترل پنل سفینه - اسباب بازی آردوینو با برش لیزری: چند ماه پیش تصمیم گرفتم که عضو فضای سازندگان محلی شوم ، زیرا مدتهاست می خواهم ابزار تجارت سازندگان را بیاموزم. من تجربه کمی از آردوینو داشتم و دوره Fusion را در اینجا در دستورالعمل ها گذراندم. با این حال من

ساعت متحرک SMART LED متصل به وب با کنترل پنل مبتنی بر وب ، زمان سرور همزمان: 11 مرحله (همراه با تصاویر)

ساعت متحرک SMART LED متصل به وب با کنترل پنل مبتنی بر وب ، Time Server Synchronized: داستان این ساعت به طولانی برمی گردد-بیش از 30 سال. پدر من وقتی 10 ساله بودم ، خیلی قبل از انقلاب LED ، پیشگام این ایده بود - زمانی که LED درخشندگی 1/1000 درخشندگی کورکننده فعلی خود را داشت. یک حقیقت

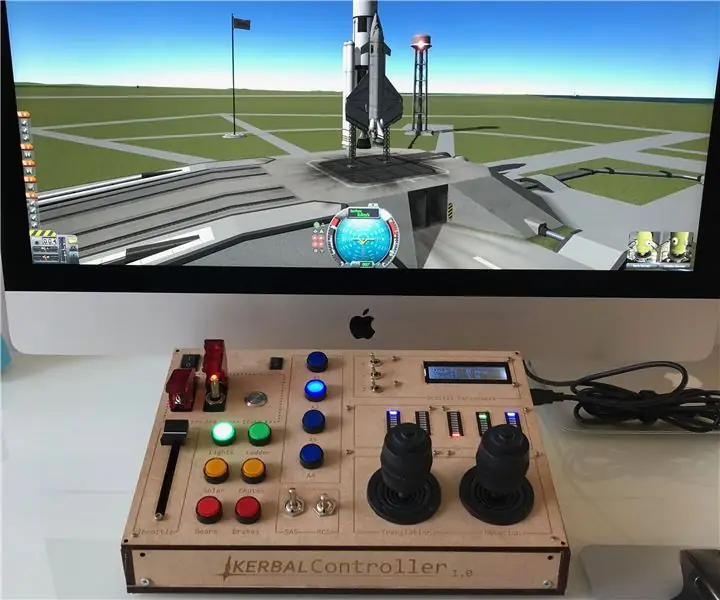

KerbalController: یک کنترل پنل سفارشی برای بازی موشکی برنامه فضایی Kerbal: 11 مرحله (همراه با تصاویر)

KerbalController: یک کنترل پنل سفارشی برای بازی موشک Kerbal Space space: چرا یک KerbalController بسازید؟ خوب ، زیرا فشار دادن دکمه ها و پرتاب سوئیچ های فیزیکی بسیار مهمتر از کلیک بر روی موس است. به خصوص هنگامی که یک سوئیچ ایمنی قرمز بزرگ است ، جایی که ابتدا باید درپوش را باز کنید ، کلید را تکان دهید