فهرست مطالب:

- مرحله 1: سخت افزار/نرم افزار را بدست آورید

- مرحله 2: بلوک نمودار

- مرحله 3: ماژول پروژه

- مرحله 4: محدودیت ها

- مرحله 5: آزمایش کنید

تصویری: VHDL کرونومتر یک دقیقه ای: 5 مرحله

2024 نویسنده: John Day | [email protected]. آخرین اصلاح شده: 2024-01-30 08:57

این آموزش نحوه ساخت کرونومتر یک دقیقه ای با استفاده از VHDL و برد Basys 3 است. چنین دستگاهی برای بازی هایی که هر بازیکن حداکثر یک دقیقه زمان برای حرکت خود دارد ایده آل است. کرونومتر ثانیه و میلی ثانیه را با دقت در صفحه هفت قسمت نمایش می دهد ، از 0 ثانیه و 0 میلی ثانیه شروع می شود ، تا 60 ثانیه و 0 میلی ثانیه. دو دکمه نیز استفاده می شود: دکمه مرکزی ، که برای شروع ، توقف و ادامه تایمر استفاده می شود و دکمه سمت راست ، برای راه اندازی مجدد تایمر استفاده می شود. وقتی دستگاه را کنار هم با کرنومتر داخلی یک تلفن هوشمند مقایسه می کنیم ، دقت ساعت قابل توجه است.

مرحله 1: سخت افزار/نرم افزار را بدست آورید

1. Basys 3 Artix-7 FPGA Trainer Board از Digilent با میکرو USB به کابل USB

2. Vivado 2016.2 Design Suite از Xilinx

مرحله 2: بلوک نمودار

این مدار از نظر رفتاری ساخته شده است و از اجزای داخلی Xilinx استفاده می کند ، اما می تواند از نظر ساختاری نیز توصیف شود ، همانطور که در نمودار ساختاری کلی بالا نشان داده شده است. از نمودار ، می توان دریافت که مدار توسط دو تقسیم فرکانس هدایت می شود. یکی از تقسیم کننده های فرکانس در 1 ثانیه اجرا می شود و شمارنده کاتدی را که به عنوان اعداد نمایش داده شده در صفحه نمایش هفت قسمتی استفاده می شود ، هدایت می کند. دومین تقسیم فرکانس با فرکانس 240 هرتز کار می کند و برای هدایت شمارنده آندی که در آندها می چرخد استفاده می شود تا همه اعداد به درستی در صفحه هفت قسمت نمایش داده شوند. رمزگذار منطق کاتد را از شمارنده کاتد و منطق آند را از شمارنده آند می گیرد و آن را به کاتد خروجی و آند که نمایشگر هفت قسمتی را اجرا می کند ، کد می کند. عملکرد این رمزگذار این است که خروجی کاتد هر بار که خروجی آند تغییر می کند تغییر کند. خروجی کاتد نمی تواند مستقل از شمارنده اجرا شود زیرا آندها باید از طریق 4 رقم جداگانه بچرخند.

مرحله 3: ماژول پروژه

در مرحله اول ، یک بلوک فرآیند برای CEN ایجاد می شود تا هنگامی که یک دکمه فشار تشخیص داده شود ، ENABLE تغییر حالت دهد. این به عنوان توقف/شروع شمارنده کاتد عمل می کند.

در بلوک فرایند بعدی ، سیگنال های ساعت سانتیم ثانیه و 240 هرتز به گونه ای تنظیم می شوند که شمارنده های مربوطه هر بار که ساعت داخلی 100 مگاهرتز به لبه صعودی می رسد ، 1 افزایش می یابد. هنگامی که شمارنده سانتیم ثانیه به 500000 برسد ، مجدداً به 0 بازنشانی می شود. در حالی که شمارنده 240 هرتز هنگامی که تعداد به 41667 برسد ، بازنشانی می شود.

در بخش کاتد کد ، اگر ENABLE '0' باشد ، شمارش کاتدها متوقف می شود. اگر دکمه تنظیم مجدد در این مدت فشار داده شود ، همه شمارش ها به "0000" بازنشانی می شود. در همین حال ، اگر ENABLE '1' باشد ، شمارش کاتد تا زمانی که تعداد کاتد به 60.00 برسد ادامه می یابد ، که در آن سیگنال توقف را 1 می کند. سیگنال توقف به بلوک فرآیند CEN باز می گردد و باعث می شود که ENABLE '0' باشد در حالی که سیگنال توقف '1' است و تا زمانی که دکمه تنظیم مجدد فشار داده نشود تغییر نمی کند.

سرانجام ، صفحه نمایش هفت قسمتی با قرار دادن 4 آند به طور صحیح با هریک از 8 کاتد خود برای نمایش همزمان ارقام مربوطه 0-9 تنظیم شده است.

مرحله 4: محدودیت ها

این فایل محدودیت ها ورودی ها و خروجی های مشخص شده از VHDL را به قسمت های ضروری و فیزیکی برد Basys متصل می کند. برای این پروژه ، اجزا شامل چهار آند و هر یک از هشت کاتد آنها برای نمایش هفت بخش ، ساعت داخلی 100 مگاهرتز ، دکمه وسط و دکمه سمت راست است.

مرحله 5: آزمایش کنید

پس از تکمیل کد ، اکنون می توانید FPGA را از طریق کابل USB برنامه ریزی کنید. صفحه نمایش هفت قسمتی باید 0.00 را نشان دهد. با فشردن دکمه مرکزی تایمر را تا زمانی که به 60.00 برسد و متوقف شود ، ببینید که آیا دکمه ها کار می کنند یا خیر. در هر زمان در بین ، می توانید دوباره دکمه مرکزی را فشار دهید تا مکث شود. پس از توقف موقت ، می توانید دکمه سمت راست را فشار دهید تا تایمر به 0.00 بازگردد. اگر همه چیز به درستی کار می کند ، تبریک می گویم شما فقط یک تایمر یک دقیقه ای ساخته اید!

توصیه شده:

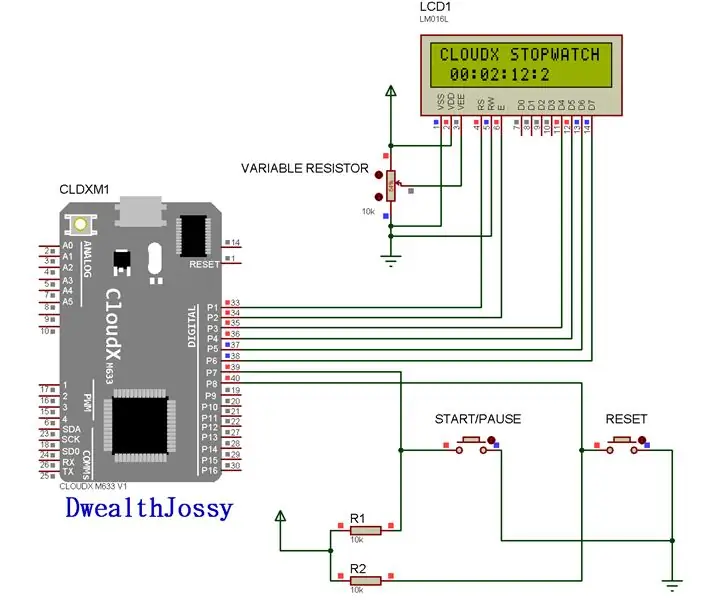

کرونومتر ساده CloudX M633: 4 مرحله

کرونومتر دیجیتالی ساده CloudX M633: در این پروژه ، ما قصد داریم نسخه ای از ساعت دیجیتالی بسازیم که می تواند ساعت ها ، دقیقه ها و ثانیه ها را ثبت کند ، درست مانند یک کرونومتر بر روی تلفن همراه شما! ما از LCD برای نمایش زمان استفاده می کنیم

کرونومتر کروکرز: 16 مرحله (همراه با تصاویر)

کرونومتر کروکرز: اگر به قورباغه ها لبخند بزنید ، برخی از آنها ارتعاش خواهند کرد. با درک حرکت ، می توان زمان را تشخیص داد-یک عمل متزلزل. قورباغه ها & quot؛ به دنبال بالا & quot؛ ساعت ها را به صورت دوتایی نشان می دهد (از چپ به راست ؛ 8،4،2،1). قورباغه ها & quot؛ چشم به راه & quot؛ نشان دهنده حداقل

کرونومتر دیجیتال همه در یک (ساعت ، تایمر ، زنگ هشدار ، دما): 10 مرحله (همراه با تصاویر)

کرونومتر دیجیتال همه در یک (ساعت ، تایمر ، زنگ هشدار ، دما): ما قصد داشتیم برای مسابقات دیگر یک تایمر بسازیم ، اما بعداً یک ساعت (بدون RTC) نیز اجرا کردیم. با شروع برنامه نویسی ، ما علاقه مند به استفاده از قابلیت های بیشتر در دستگاه شدیم و در نهایت DS3231 RTC را اضافه کردیم ، به عنوان

کرونومتر اولیه با استفاده از VHDL و Basys3 Board: 9 مرحله

کرونومتر پایه با استفاده از VHDL و برد Basys3: به نحوه آموزش ساخت کرنومتر با استفاده از برد پایه VHDL و Basys 3 خوش آمدید. ما مشتاق هستیم که پروژه خود را با شما به اشتراک بگذاریم! این آخرین پروژه برای دوره CPE 133 (طراحی دیجیتال) در Cal Poly ، SLO در پاییز 2016 بود. پروژه ای که ما در حال ساخت آن هستیم

کرونومتر VHDL: 8 مرحله (همراه با تصاویر)

کرونومتر VHDL: این آموزش نحوه ایجاد کرونومتر با استفاده از VHDL و برد FPGA است ، مانند برد Basys3 Atrix-7. کرونومتر قادر است از 00.00 ثانیه تا 99.99 ثانیه شمارش کند. از دو دکمه استفاده می کند ، یکی برای دکمه شروع/توقف و دیگری برای